Benchmarq... The brains behind the battery. TM

# 1997 Data Book

BENCHMARQ® Microelectronics, Inc. 17919 Waterview Parkway Dallas, Texas 75252 Fax: (972) 437-9198 Tel: (972) 437-9195

E-mail: benchmarq@benchmarq.com World Wide Web: http://www.benchmarq.com

### **BENCHMARQ 1997 Data Book**

Copyright © 1997, BENCHMARQ Microelectronics, Inc. All rights reserved.

No part of this book may be reproduced in any form or means, without express permission from Benchmarq.

This data book contains new product information. Benchmarq reserves the right to make changes in its products without notice.

Benchmarq assumes no responsibility for use of any products or circuitry described within. No license for use of intellectual property (patents, copyrights, or other rights) owned by Benchmarq or other parties is granted or implied.

Benchmarq does not authorize the use of its components in life-support systems where failure or malfunction may cause injury to the user. If Benchmarq components are used in life-support systems, the user assumes all responsibilities and indemnifies Benchmarq from all liability or damages.

Benchmarq is a registered trademark, and "Benchmarq . . . . The brains behind the battery" and Power Gauge are trademarks of BENCHMARQ Microelectronics, Inc.

IBM is a registered trademark of International Business Machine Corporation. U.L. is a registered trademark of Underwriters Laboratory. Rayovac and Renewal are registered trademarks of Rayovac Corporation.

Printed in U.S.A.

## **Our Products**

At Benchmarq, we provide integrated circuit and module solutions for power-sensitive and portable electronics systems.

Power-sensitive AC-powered systems in the office and industry must gracefully deal with the loss of power, maintaining the integrity of important data and self-sufficiently continuing critical operation. Portable systems share the design requirements of their powercord-bound counterparts, but add entirely new challenges—including power supervision, energy management, data security, and size minimization.

The product families described in this data book directly address these requirements, taking full advantage of advanced analog and digital VLSI technologies and state-of-the-art battery and packaging expertise. Power supervision, energy management, size reduction, nonvolatility, data security, and retrofit capability are integral to Benchmarq's product line.

## **Our Commitment**

When you choose to integrate Benchmarq products within your own, be assured that Benchmarq is committed to providing the specific solutions you need today and to developing creative solutions to the growing challenges of tomorrow—supported by the best customer service and the highest overall quality.

The drive for excellence in all dimensions of quality is a cornerstone of our company.

## **Data Book Organization**

This data book is organized into general information sections and product family sections.

You can locate information in this book in several ways.

| To locate information by:           | See pages:   |  |  |

|-------------------------------------|--------------|--|--|

| Table of Contents                   | v – vii      |  |  |

| Alphanumeric Product Index          | viii – ix    |  |  |

| Family Summary and Selection Guides | x – xvi      |  |  |

| Product Cross-Reference Tables      | xvii – xviii |  |  |

| Ordering Information                | хіх          |  |  |

| Data Sheet Types                    | xx           |  |  |

Chapters 1 through 6 contain detailed product information. Chapter 7 includes packaging information, and Chapter 8 describes Benchmarq's commitment to quality and the processes we use to ensure reliability in our products. Chapter 9 lists sales offices and distributors.

## For More Information ...

If you haven't found it here . . . Ask!

Benchmarq maintains an updated product listing on the World Wide Web at the URL listed below. Browse the Benchmarq Home Page for the latest Benchmarq product information and sales office locations at:

#### http://www.benchmarq.com

To send us e-mail to be added to our mailing list or to get further information, contact Benchmarq at:

#### benchmarq@benchmarq.com

Additional Benchmarq information is available from your Benchmarq distributor or sales office (listed in the back of this Data Book), or by contacting Benchmarq Customer Service at (800) 966-0011 or (972) 437-9195.

| Alphanumeric Product Index                                             | wiii   |

|------------------------------------------------------------------------|--------|

| Family Summary and Selection Guides                                    | , VIII |

| Product Cross-Reference Tables                                         |        |

| Ordering Information                                                   |        |

| Data Sheet Types                                                       |        |

| Data Sneet Types                                                       | AA     |

| TI 4 Ol a seeta IO                                                     | 1      |

| Fast Charge ICs                                                        | 1      |

| bq2002 Fast Charge IC                                                  |        |

| bq2002C Fast Charge IC                                                 |        |

| bq2002T Fast Charge IC With ΔT/Δt                                      |        |

| DV2002L2/TL2 Fast Charge Development System                            |        |

| bq2003 Fast Charge IC                                                  |        |

| DV2003L1 Fast Charge Development System                                |        |

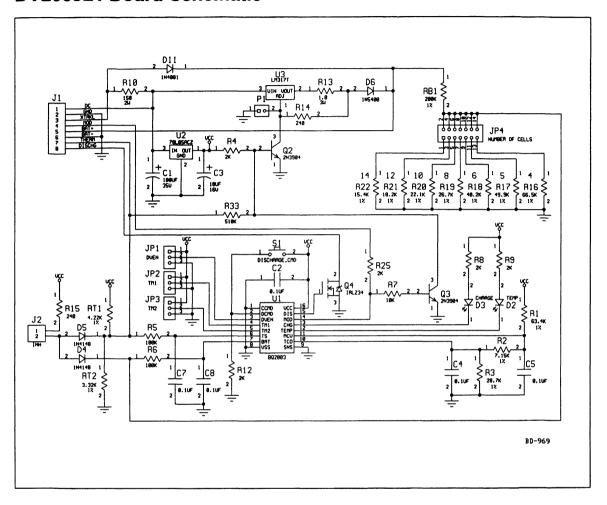

| DV2003L3 Fast Charge Development System                                | 1-45   |

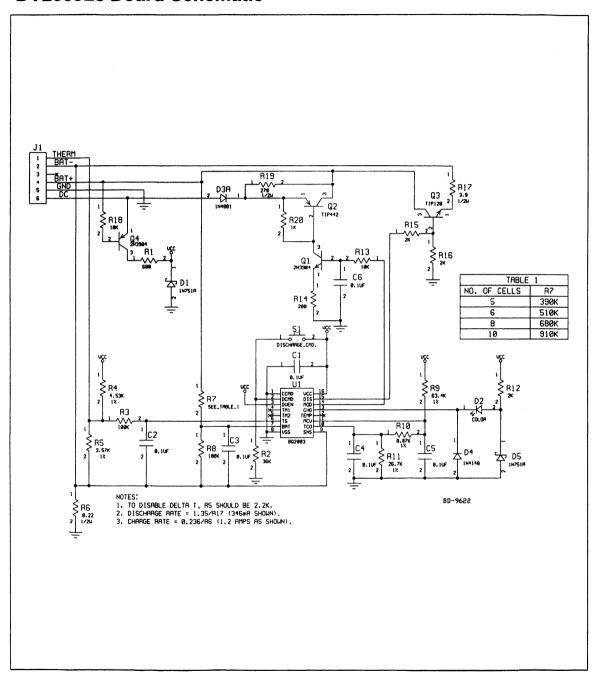

| DV2003S1 Fast Charge Development System                                | 1-47   |

| DV2003S2 Fast Charge Development System                                |        |

| Application Note: "Using the bq2003 to Control Fast Charge"            | 1-51   |

| Application Note: "Step-Down Switching Current Regulation              |        |

| Using the bq2003 Fast Charge IC"                                       | 1-69   |

| Application Note: "Using the bq2003 With High-Side Current             |        |

| Sensing in a Switch-Mode Charger"                                      | 1-85   |

| bq2004 Fast Charge IC                                                  | 1-87   |

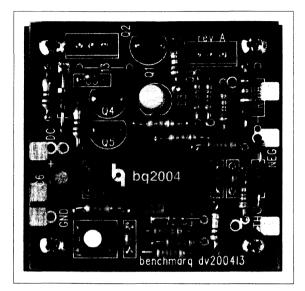

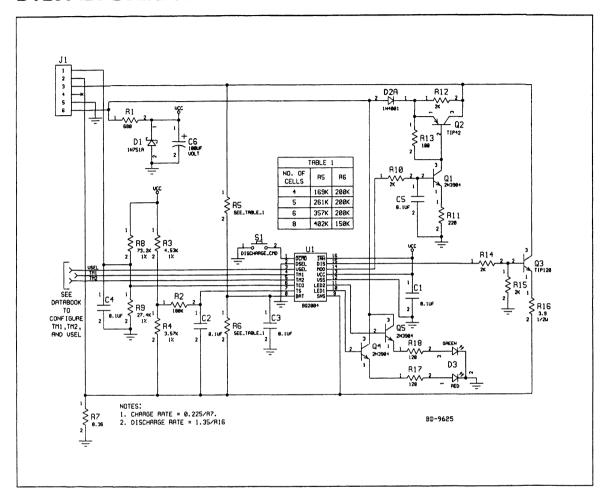

| DV2004L1 Fast Charge Development System                                | 1-101  |

| DV2004L3 Fast Charge Development System                                |        |

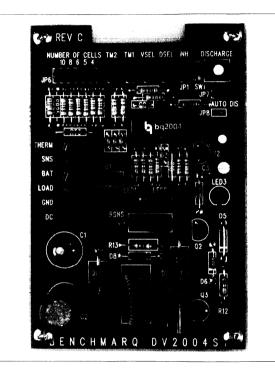

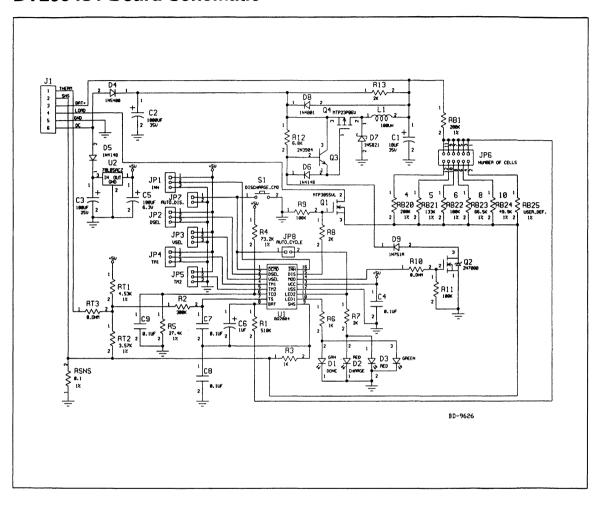

| DV2004S1 Fast Charge Development System                                | 1-105  |

| DV2004S3 Nickel/Li-Ion Development System                              |        |

| bq2004E Fast Charge IC                                                 |        |

| DV2004ES1 Fast Charge Development System                               | 1-125  |

| DV2004ES3 Nickel/Li-Ion Development System                             |        |

| bq2005 Dual-Battery Fast Charge IC                                     |        |

| DV2005L1 Fast Charge Development System                                | -      |

| DV2005S1 Fast Charge Development System                                |        |

| DV2005S3 Nickel/Li-Ion Development System                              |        |

| Application Note: "Using the bq2005 to Control Fast Charge"            | 1-153  |

| bq2007 Fast Charge IC                                                  |        |

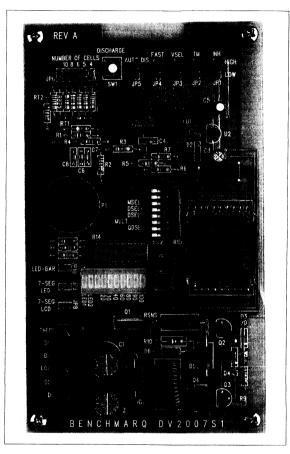

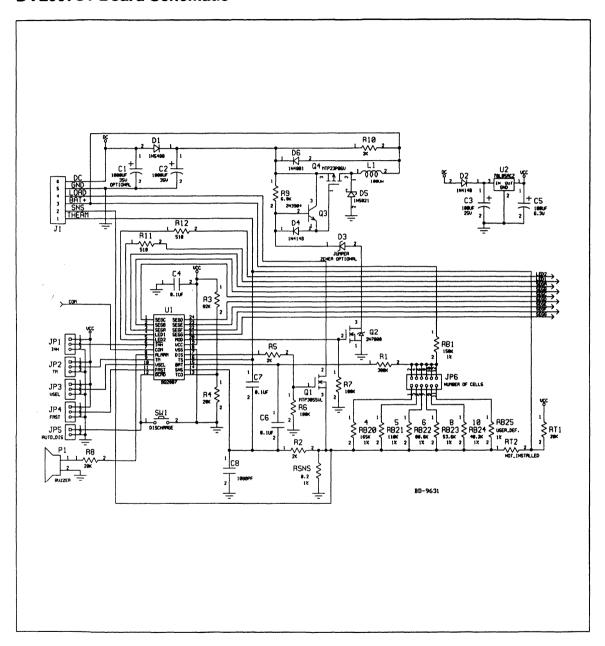

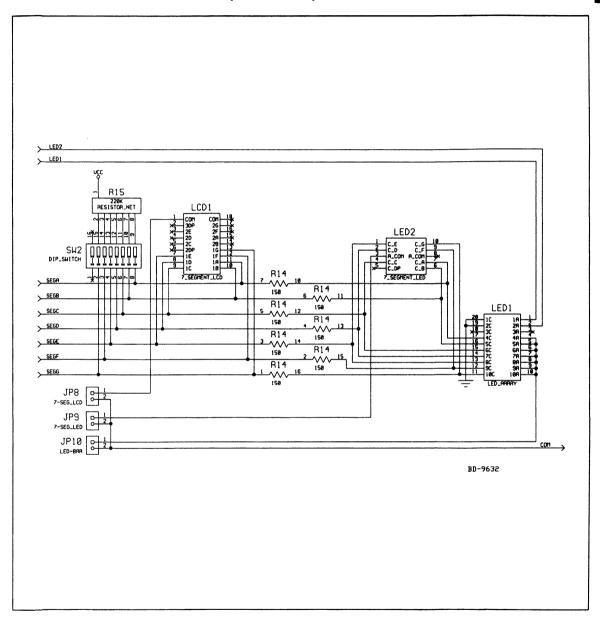

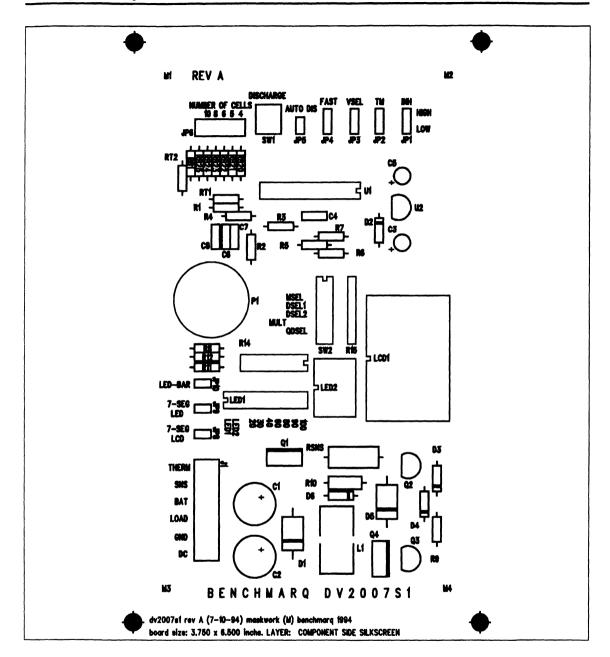

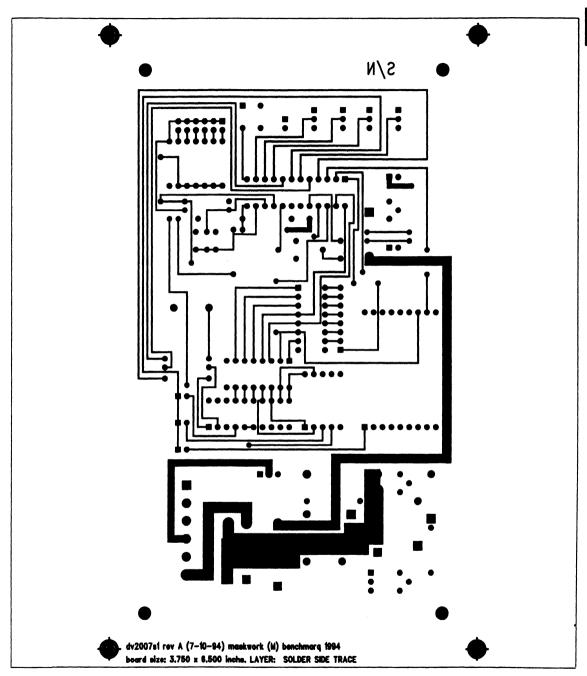

| DV2007S1 Fast Charge Development System                                |        |

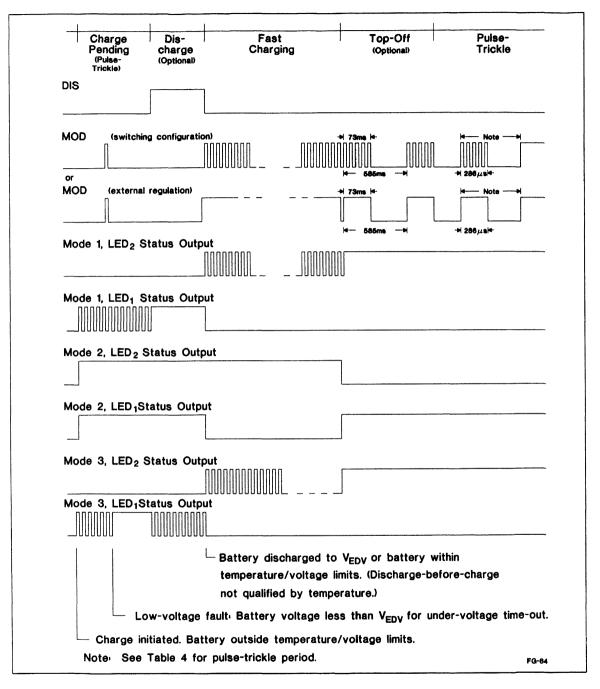

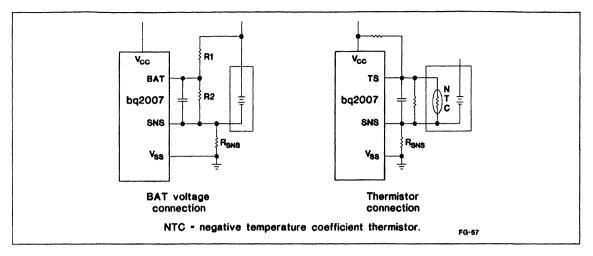

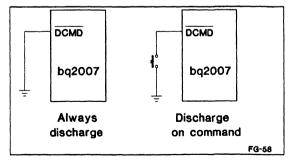

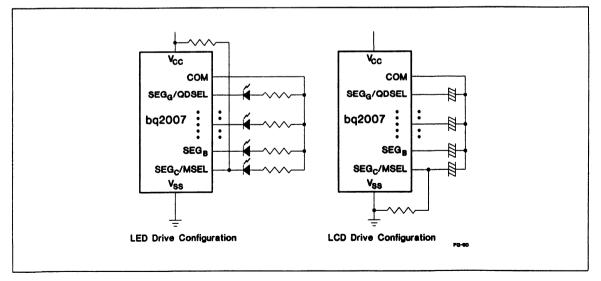

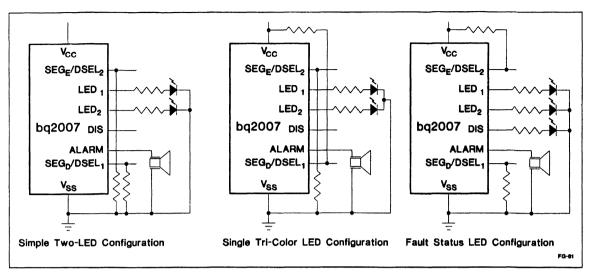

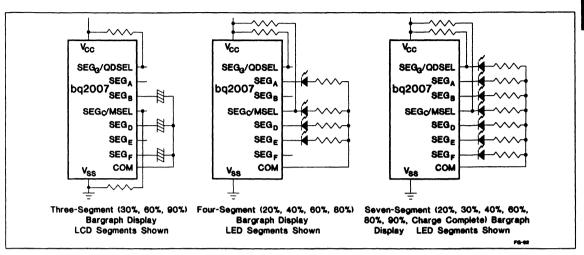

| Application Note: "Using the bq2007 Display Mode Options"              |        |

| Application Note: "Using the bq2007 Enhanced Features for Fast Charge" |        |

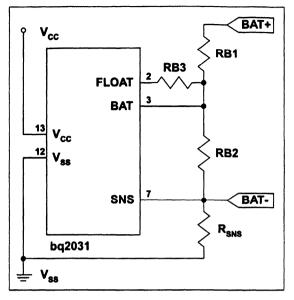

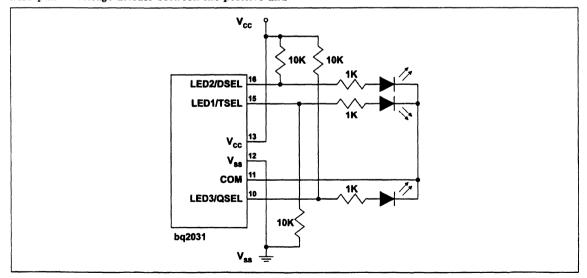

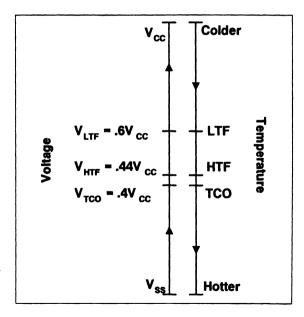

| bq2031 Lead-Acid Fast Charge IC                                        |        |

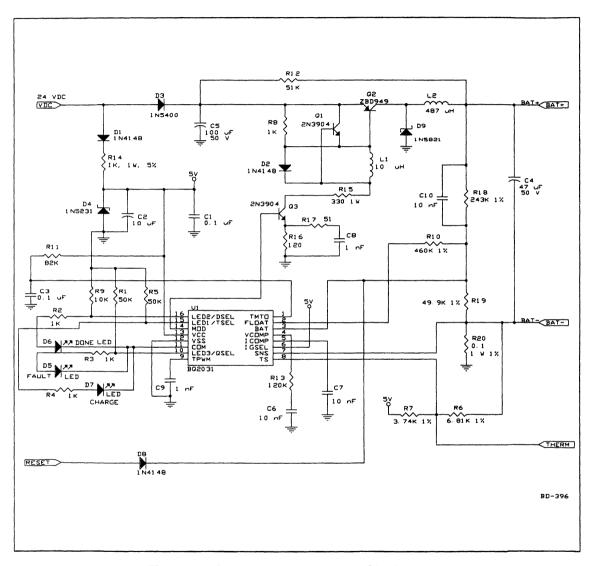

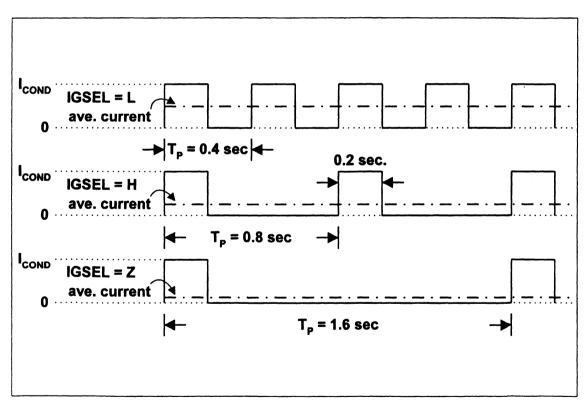

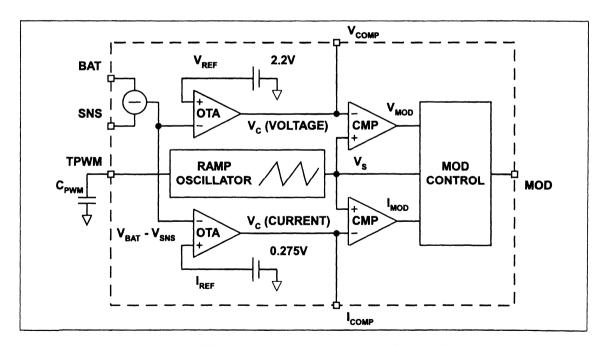

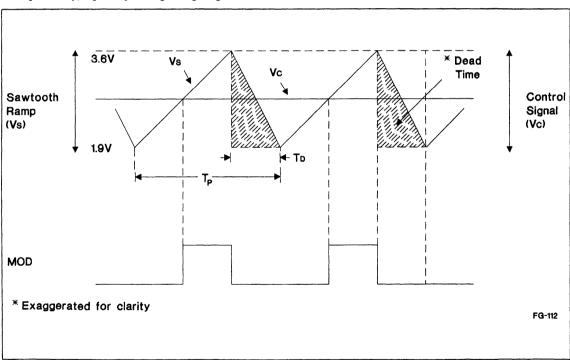

| DV2031S1 Fast Charge Development System                                |        |

| Application Note: "Using the bq2031 to Charge Lead-Acid Batteries"     | 1-995  |

| Application Note: "Switch-Mode Power Conversion Using the bq2031"      |        |

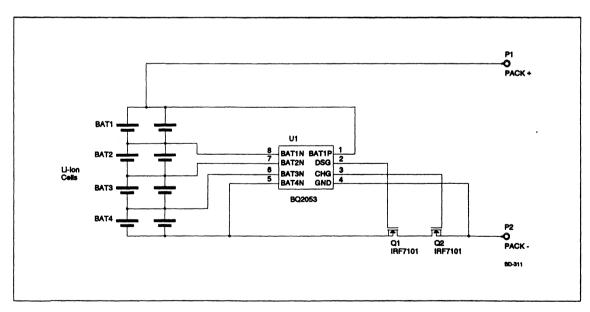

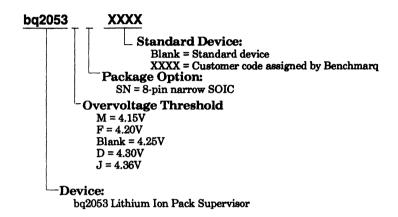

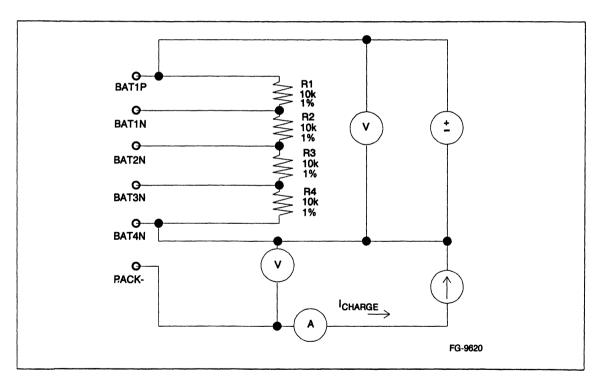

| bq2053 Lithium Ion Pack Supervisor                                     |        |

| Application Note: "Using the bq2053 Lithium Ion Pack Supervisor"       | 1 965  |

| bq2054 Lithium Ion Fast Charge IC                                      |        |

|                                                                        |        |

| DV2054S1 Fast Charge Development System                                |        |

| EV205x bq2050, bq2053, and bq2004/E Li-Ion Evaluation System           |        |

| bq2058 Lithium Ion Pack Supervisor                                     |        |

| bq2902 Rechargeable Alkaline Charge IC                                 |        |

| bq2903 Rechargeable Alkaline Charge IC                                 |        |

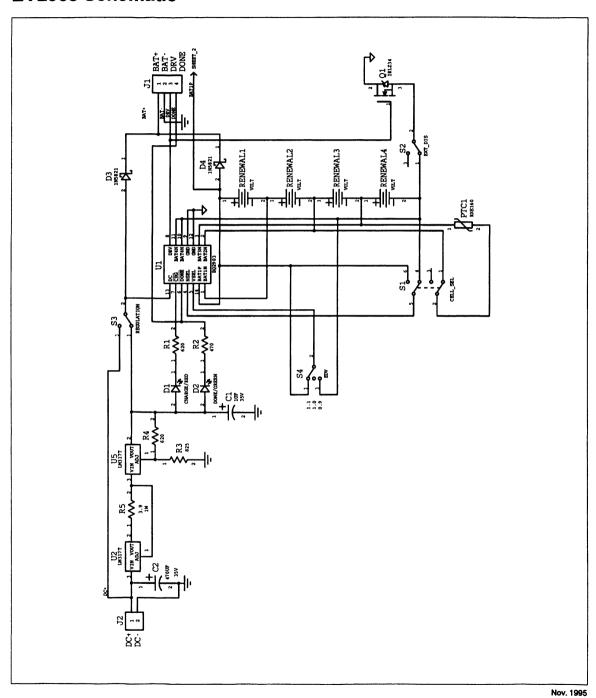

| EV2903 bq2903 Evaluation System                                        | 1-323  |

## **Table of Contents**

| Gas Gauge ICs bq2010 Gas Gauge IC                                            | <b>2</b>    |

|------------------------------------------------------------------------------|-------------|

| EV2010 bq2010 Evaluation System                                              | 2-1<br>9 10 |

| Application Note: "Using the bq2010 A Tutorial for Gas Gauging"              |             |

| bq2011 Gas Gauge IC                                                          |             |

| EV2011 bq2011 Evaluation System                                              |             |

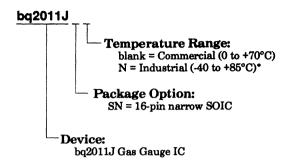

| bq2011J Gas Gauge IC                                                         |             |

| bq2011K Gas Gauge IC                                                         |             |

| EV2011J/K bq2011J/K Evaluation System                                        |             |

| bq2012 Gas Gauge IC                                                          |             |

| EV2012 bq2012 Evaluation System                                              |             |

| bq2014 Gas Gauge IC With External Charge Control                             |             |

| bq2014H Gas Gauge IC With External Charge Control                            |             |

| EV2014 bq2014 Evaluation Board                                               |             |

| EV2014x Gas Gauge and Fast Charge Evaluation System                          |             |

| Application Note: "Using NiMH and Li-Ion Batteries in Portable Applications" |             |

| DV2043S7 Level 2 Smart Charger With Dual Battery Selector                    |             |

| bq2040 Gas Gauge IC With SMBus Interface                                     |             |

| bq2050 Lithium Ion Power Gauge™ IC                                           |             |

| bq2050H Lithium Ion Power Gauge™ IC                                          |             |

| EV2050 Power Gauge Evaluation Board                                          |             |

| bq2090 Gas Gauge IC With SMBus v.95 Interface                                |             |

| bq2091 Gas Gauge IC With SMBus v.95 Interface                                |             |

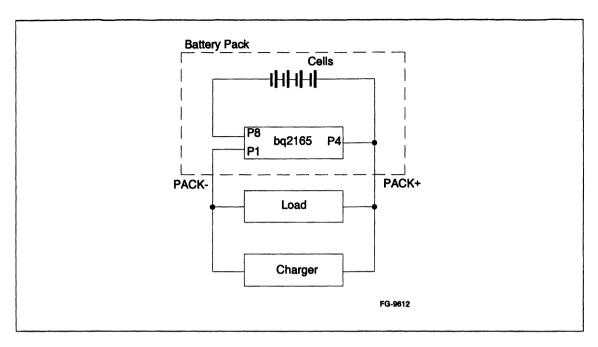

| Battery Management Board-Level Products                                      | 3           |

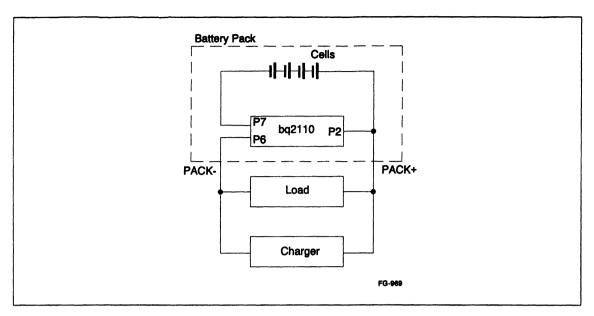

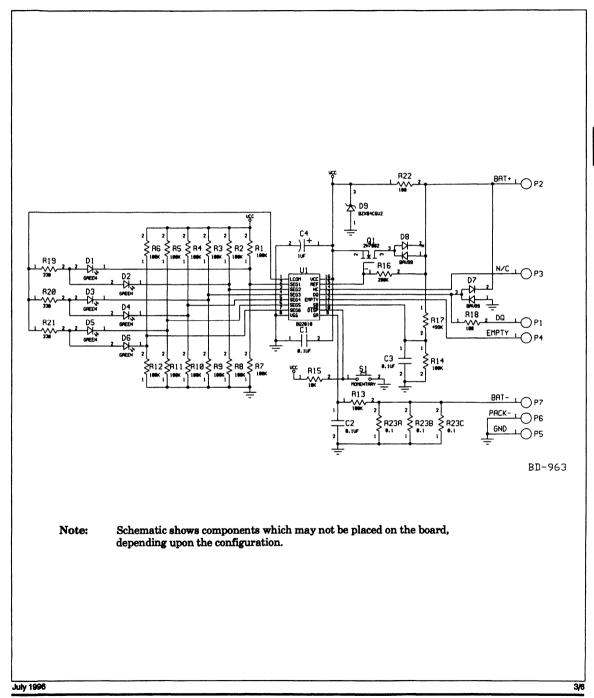

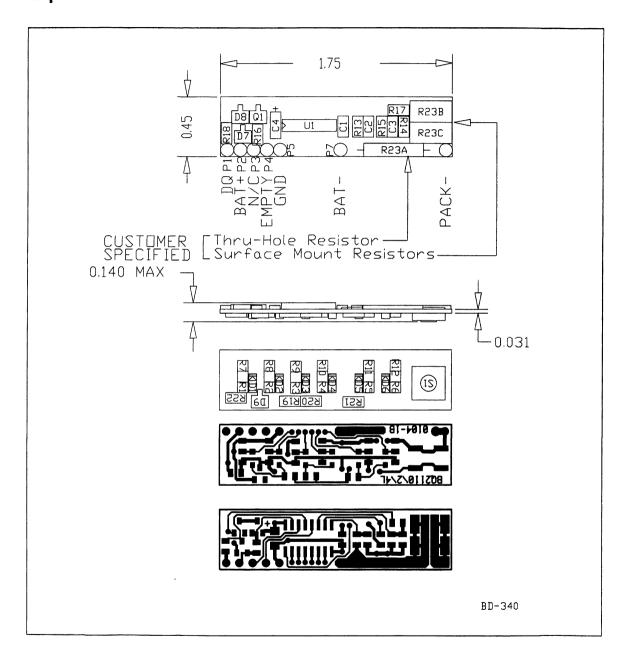

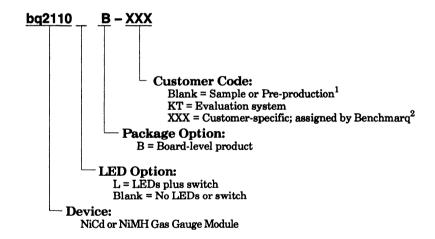

| bq2110/L NiCd or NiMH Gas Gauge Module                                       | 3-1         |

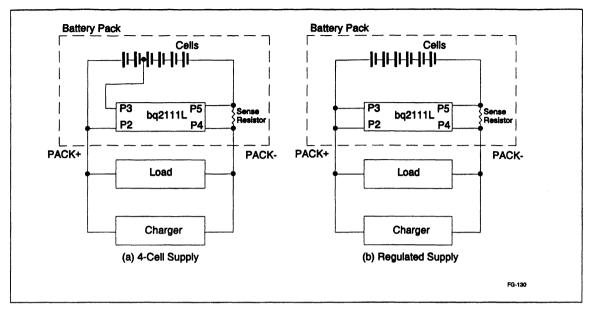

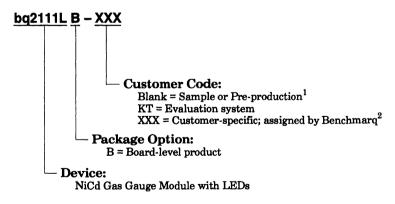

| bq2111L NiCd Gas Gauge Module With LEDs                                      |             |

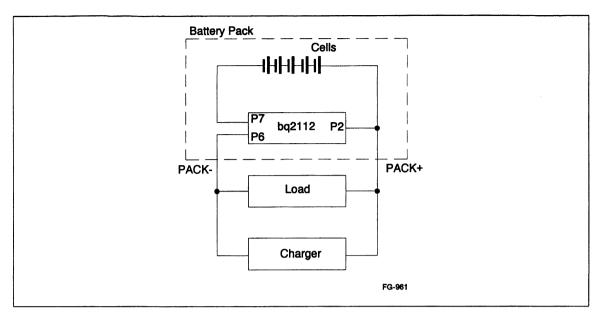

| bq2112/L NiCd or NiMH Gas Gauge Module With Slow Charge Control              |             |

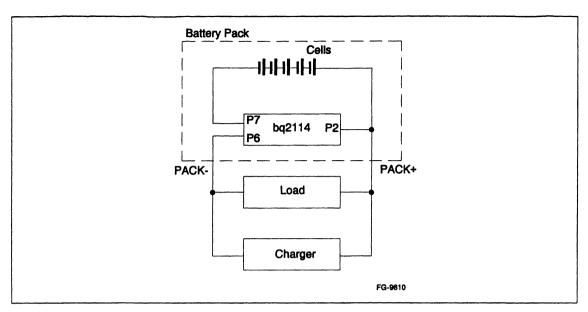

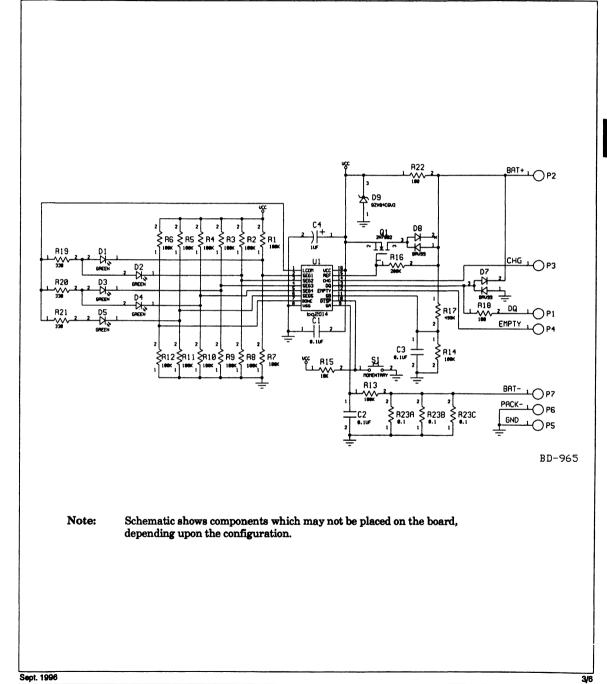

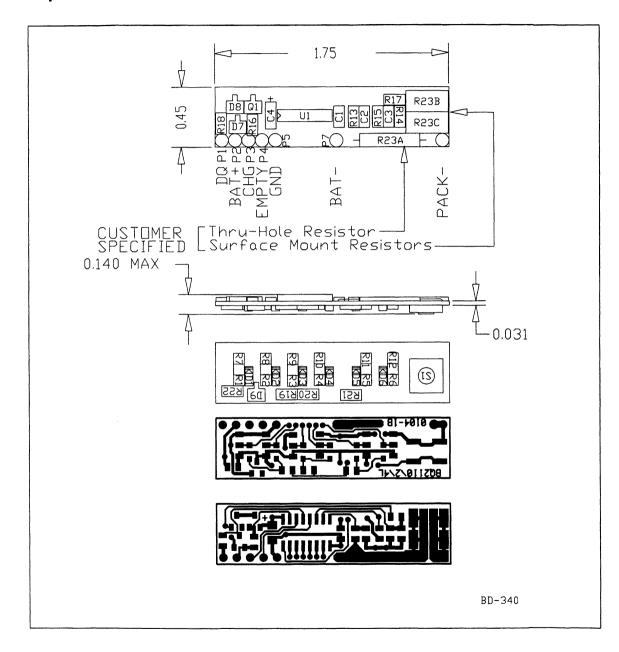

| bq2114/L NiCd or NiMH Gas Gauge Module With Charge Control Output            | 3-19        |

| bq2150/L Lithium Ion Power Gauge Module                                      | 3-25        |

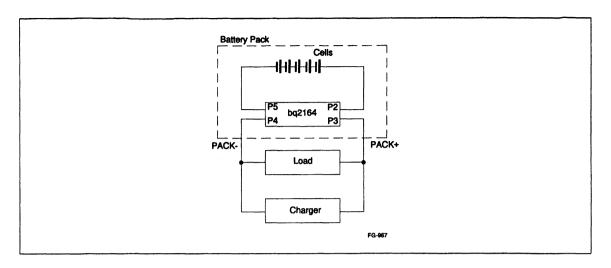

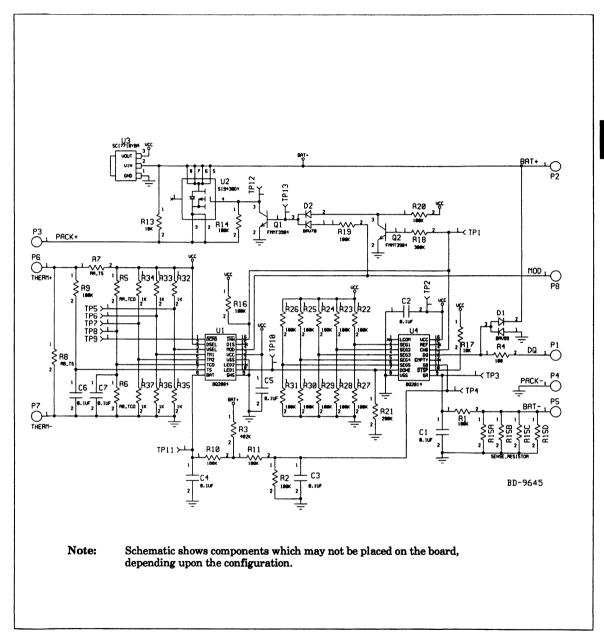

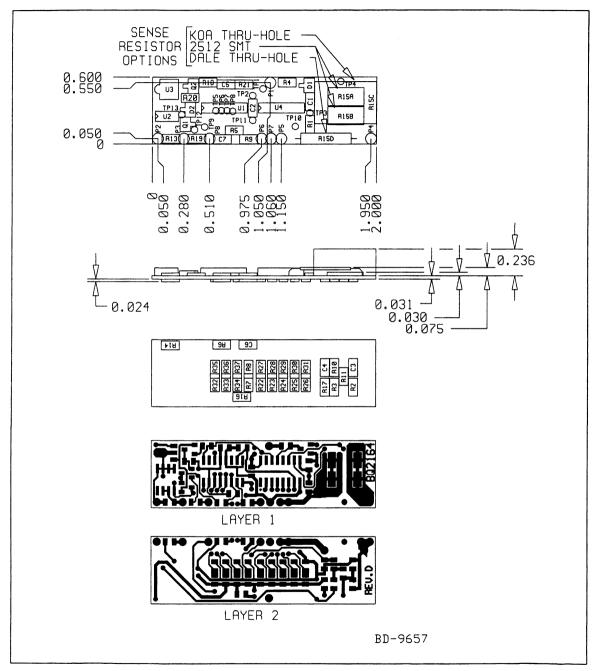

| bq2153 Lithium Ion Pack Supervisor Module                                    | 3-31        |

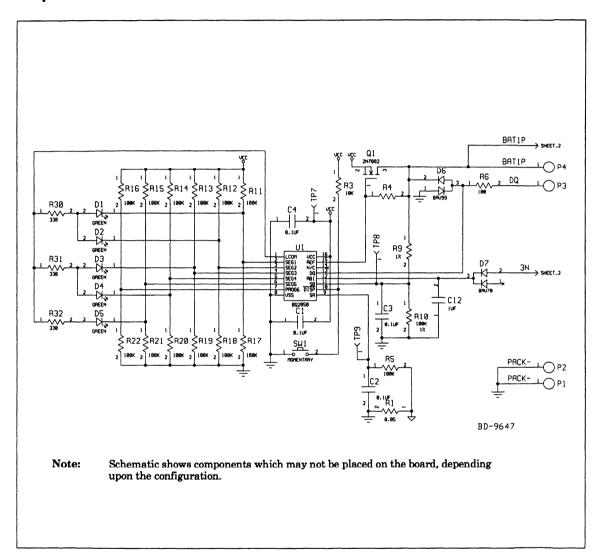

| bq2164 NiCd or NiMH Gas Gauge Module With Fast Charge Control                | 3-37        |

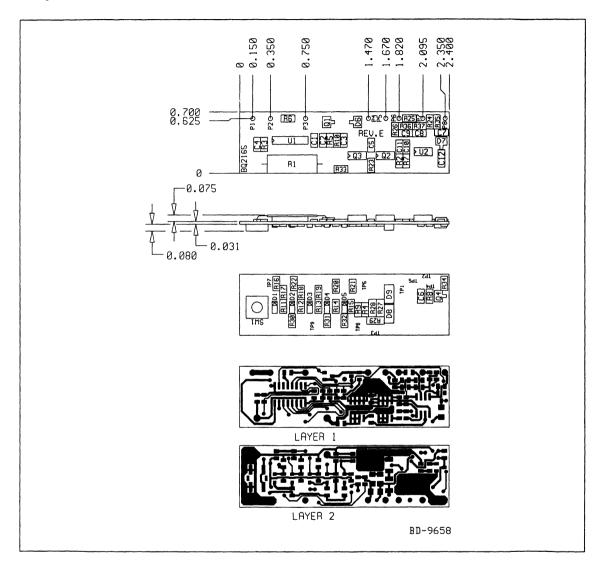

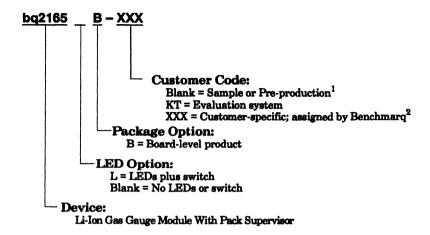

| bq2165/L Li-Ion Gas Gauge Module With Pack Supervision                       | 3-45        |

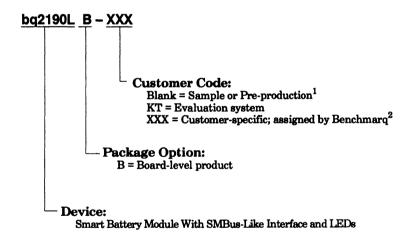

| bq2190L Smart Battery Module With SMBus v.95 Interface and LEDs              | 3-55        |

| bq2193L Rechargeable Alkaline Charger Module                                 | 3-61        |

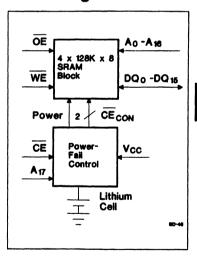

| Static RAM Nonvolatile Controllers                                           | 4           |

| bq2201 Nonvolatile Controller (by one)                                       | 4-1         |

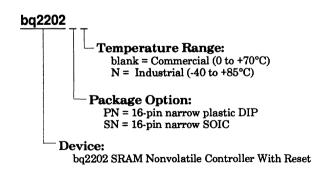

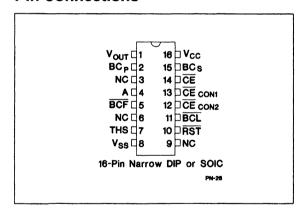

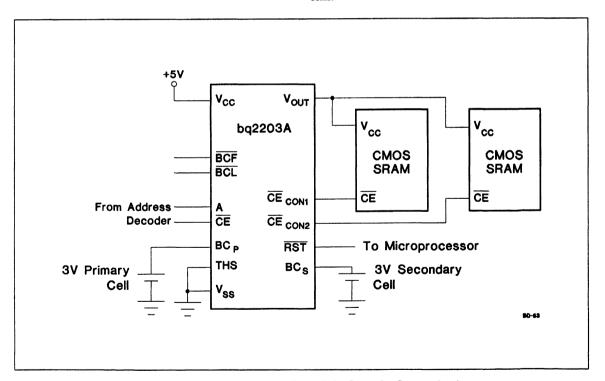

| bq2202 SRAM Nonvolatile Controller With Reset                                |             |

| bq2203A Nonvolatile Controller With Battery Monitor                          |             |

| bq2204A Nonvolatile Controller (by four)                                     |             |

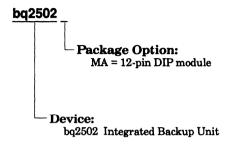

| bg2502 Integrated Backup Unit                                                | 4-33        |

| Real-Time Clocks                                                         | 5    |

|--------------------------------------------------------------------------|------|

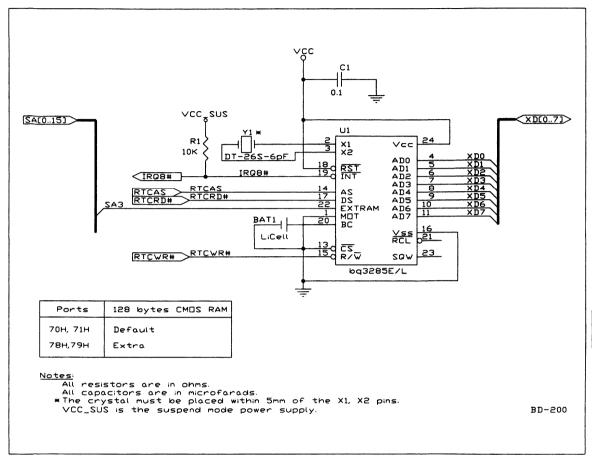

| bq3285 Real-Time Clock IC                                                |      |

| bq3285E/L Real-Time Clock IC                                             |      |

| bq3285EC/LC Real-Time Clock IC                                           |      |

| bq3287/bq3287A Real-Time Clock Module                                    |      |

| bq3287E/bq3287EA Real-Time Clock Module                                  |      |

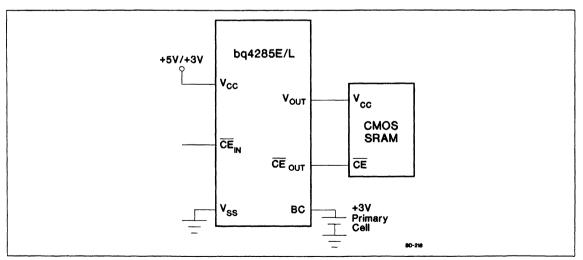

| bq4285 Real-Time Clock With NVRAM Control                                |      |

| bq4285E/L Enhanced RTC With NVRAM Control                                |      |

| bq4287 Real-Time Clock Module With NVRAM Control                         |      |

| bq4287E Enhanced RTC Module With NVRAM Control                           |      |

| bq4830Y RTC Module With 32Kx8 NVSRAM                                     |      |

| bq4832Y RTC Module With 32Kx8 NVSRAM                                     |      |

| bq4842Y RTC Module With 128Kx8 NVSRAM                                    | 5-16 |

| bq4845/Y Parallel RTC With CPU Supervisor                                | 5-18 |

| bq4847/Y RTC Module With CPU Supervisor                                  | 5-19 |

| bq4850Y RTC Module With 512Kx8 NVSRAM                                    |      |

| bq4852Y RTC Module With 512Kx8 NVSRAM                                    | 5-21 |

| Application Note: "Using the bq4845 for a Low-Cost RTC/NVSRAM Subsystem" | 5-23 |

| Application Note: "Typical PC Hookups for RTCs"                          | 5-24 |

| Application Note: "Using RAM Clear Function"                             | 5-25 |

| Application Note: "Time-Base Oscillator"                                 |      |

| Application Note: "Using bq3285E/L in a Green or Portable Environment"   | 5-26 |

| Nonvolatile Static RAM                                                   | 6    |

| bq4010/Y—8K x 8 Nonvolatile SRAM                                         |      |

| bq4011/Y—32K x 8 Nonvolatile SRAM                                        |      |

| bq4013/Y—128K x 8 Nonvolatile SRAM                                       |      |

| bq4014/Y-256K x 8 Nonvolatile SRAM                                       | 6-31 |

| bq4015/Y—512K x 8 Nonvolatile SRAM                                       |      |

| bq4016/Y—1024Kx8 Nonvolatile SRAM                                        | 6-51 |

| bq4017/Y—2048Kx8 Nonvolatile SRAM                                        | 6-61 |

| bq4024/Y—128K x 16 Nonvolatile SRAM                                      |      |

| bq4025/Y—256K x 16 Nonvolatile SRAM                                      |      |

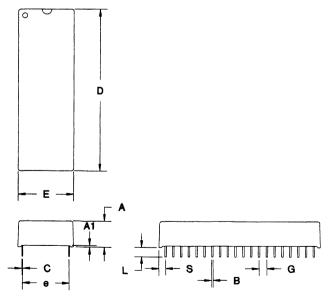

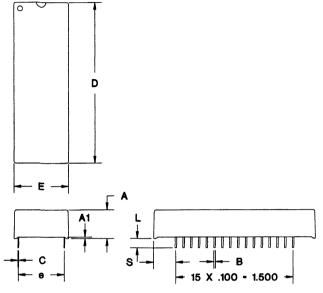

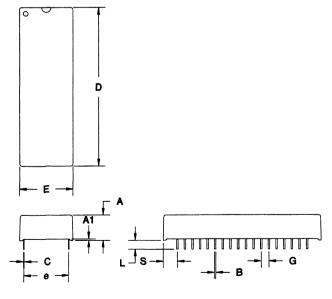

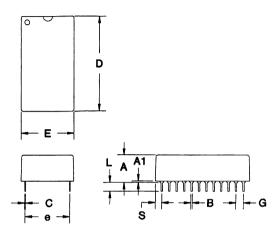

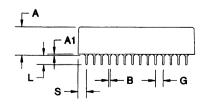

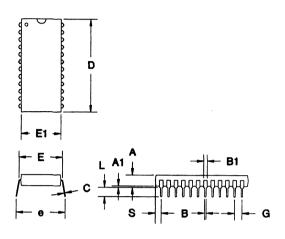

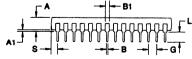

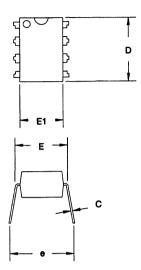

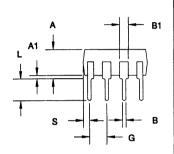

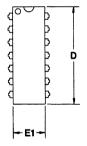

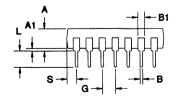

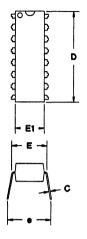

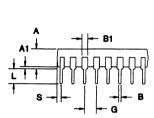

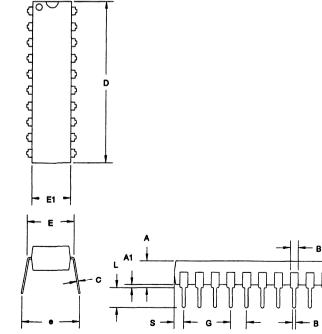

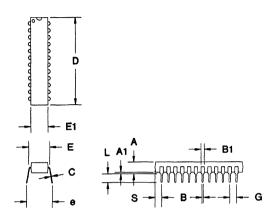

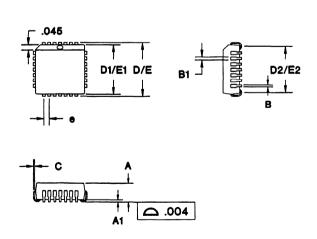

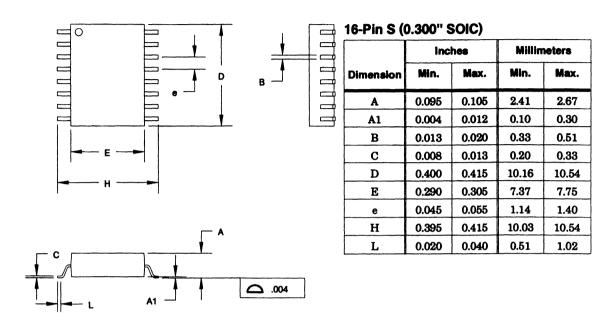

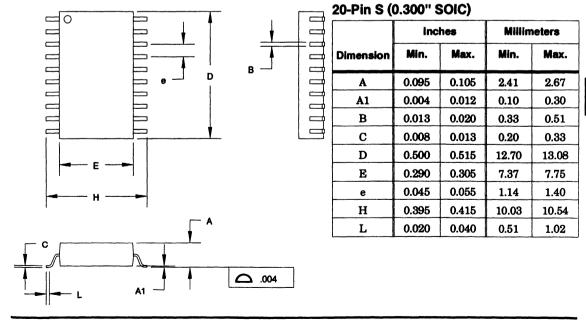

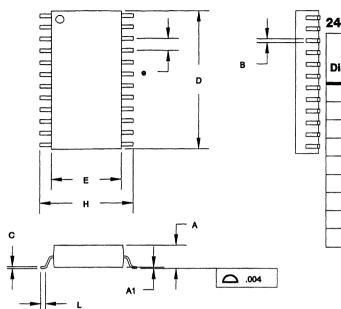

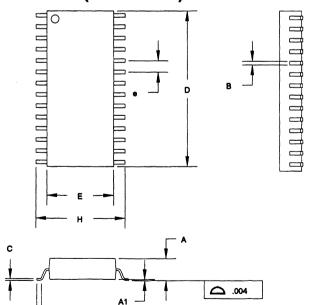

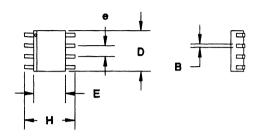

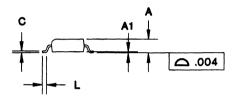

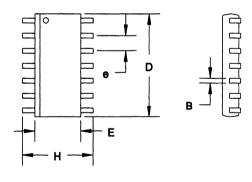

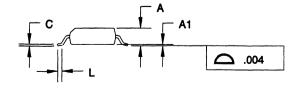

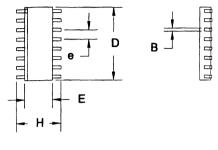

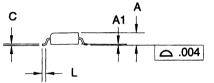

| Package Drawings                                                         | 7    |

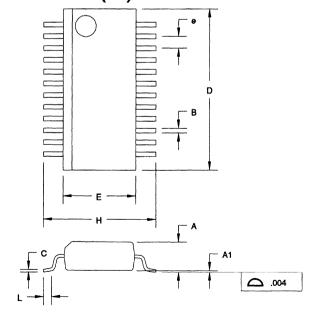

| Quality and Reliability                                                  | 8    |

| Salas Offices and Distributors                                           | ۵    |

## **Table of Contents**

| Part No.         | Description                                                                   |       |  |  |  |

|------------------|-------------------------------------------------------------------------------|-------|--|--|--|

| bq2002           | Fast Charge IC                                                                | 1-1   |  |  |  |

| bq2002C          | Fast Charge IC                                                                | 1-11  |  |  |  |

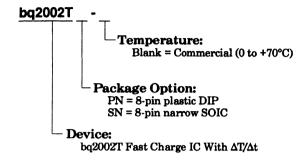

| bq2002T          | Fast Charge IC With ΔT/Δt                                                     | 1-19  |  |  |  |

| bq2003           | Fast Charge IC                                                                | 1-31  |  |  |  |

| bq2004           | Fast Charge IC                                                                | 1-87  |  |  |  |

| bq2004E          | Fast Charge IC                                                                | 1-111 |  |  |  |

| bq2005           | Dual-Battery Fast Charge IC                                                   | 1-131 |  |  |  |

| bq2007           | Fast Charge IC                                                                | 1-171 |  |  |  |

| bq2010           | Gas Gauge IC                                                                  | 2-1   |  |  |  |

| bq2011           | Gas Gauge IC                                                                  | 2-29  |  |  |  |

| bq2011J          | Gas Gauge IC                                                                  | 2-51  |  |  |  |

| bq2011K          | Gas Gauge IC                                                                  | 2-69  |  |  |  |

| bq2012           | Gas Gauge/Fast Charge IC                                                      | 2-89  |  |  |  |

| bq2014           | Gas Gauge IC With External Charge Control                                     | 2-111 |  |  |  |

| bq2014H          | Gas Gauge IC With External Charge Control                                     | 2-131 |  |  |  |

| bq2031           | Charge IC for Lead Acid Batteries                                             | 1-209 |  |  |  |

| bq2040           | Gas Gauge IC With SMBus Interface                                             | 2-149 |  |  |  |

| bq2050           | Gas Gauge IC With SMBus Interface<br>Lithium Ion Power Gauge <sup>TM</sup> IC | 2-179 |  |  |  |

| bq2050H          | Lithium Ion Power Gauge <sup>TM</sup> IC                                      | 2-199 |  |  |  |

| bq2053           | Lithium Ion Pack Supervisor IC                                                | 1-257 |  |  |  |

| bq2054           | Lithium Ion Fast Charge IC                                                    | 1-273 |  |  |  |

| bq2054           | Lithium Ion Pack Supervisor IC                                                | 1-273 |  |  |  |

| bq2090           | Gas Gauge IC With SMBus v.95 Interface                                        | 2-221 |  |  |  |

| bq2091           | Gas Gauge IC With SMBus v.95 Interface                                        | 2-221 |  |  |  |

| -                |                                                                               |       |  |  |  |

| bq2110/L         | NiCd or NiMH Gas Gauge Module                                                 | 3-1   |  |  |  |

| bq2111L          | NiCd Gas Gauge Module With LEDs                                               | 3-7   |  |  |  |

| bq2112/L         | NiCd or NiMH Gas Gauge Module/Slow Charge Control                             | 3-13  |  |  |  |

| bq2114/L         | NiCd or NiMH Gas Gauge Module/Charge Control Output                           | 3-19  |  |  |  |

| bq2150/L         | Lithium Ion Power Gauge Module                                                | 3-25  |  |  |  |

| bq2153           | Lithium Ion Pack Supervisor Module                                            | 3-31  |  |  |  |

| bq2164           | NiCd or NiMH Gas Gauge Module/Fast Charge Control                             | 3-37  |  |  |  |

| bq2165/L         | Lithium Ion Gas Gauge Module With Pack Supervision                            | 3-45  |  |  |  |

| bq2190L          | Smart Battery Module With SMBus v.95 Interface and LEDs                       | 3-55  |  |  |  |

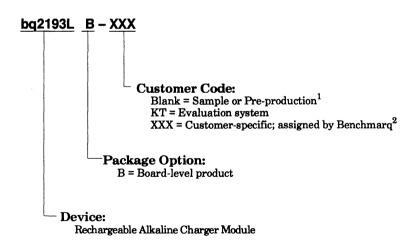

| bq2193L          | Rechargeable Alkaline Charger Module                                          | 3-61  |  |  |  |

| h-0001           | No conduct to CDAM Controlled by Con                                          | 4.1   |  |  |  |

| bq2201           | Nonvolatile SRAM Controller, by One                                           | 4-1   |  |  |  |

| bq2202           | SRAM Nonvolatile Controller With Reset                                        | 4-9   |  |  |  |

| bq2203A          | Nonvolatile Controller With Battery Monitor                                   | 4-17  |  |  |  |

| bq2204A          | Nonvolatile SRAM Controller, by Four                                          | 4-25  |  |  |  |

| bq2502           | Integrated Backup Unit                                                        | 4-33  |  |  |  |

| bq2902           | Rechargeable Alkaline Charge IC                                               | 1-305 |  |  |  |

| bq2903           | Rechargeable Alkaline Charge IC                                               | 1-313 |  |  |  |

| bq3285           | Real-Time Clock IC                                                            | 5-1   |  |  |  |

| bq3285E/L        |                                                                               |       |  |  |  |

| bq3285EC/LC      | Real-Time Clock IC, Enhanced                                                  | 5-21  |  |  |  |

| bq3287/bq3287A   | Real-Time Clock IC                                                            | 5-45  |  |  |  |

| bq3287E/bq3287EA | Real-Time Clock Module                                                        | 5-69  |  |  |  |

| DQU401E/DQU401EA | Real-Time Clock Module, Enhanced                                              | 5-73  |  |  |  |

# **Alphanumeric Product Index**

| Part No.  | Description                                          | Page  |

|-----------|------------------------------------------------------|-------|

| bq4010    | 8Kx8 Nonvolatile SRAM                                | 6-1   |

| bq4011    | 32Kx8 Nonvolatile SRAM                               | 6-11  |

| bq4013    | 128Kx8 Nonvolatile SRAM                              | 6-21  |

| bq4014    | 256Kx8 Nonvolatile SRAM                              | 6-31  |

| bq4015    | 512Kx8 Nonvolatile SRAM                              | 6-41  |

| bq4016    | 1024Kx8 Nonvolatile SRAM                             | 6-51  |

| bq4017    | 2048Kx8 Nonvolatile SRAM                             | 6-61  |

| bq4024    | 128Kx16 Nonvolatile SRAM                             | 6-71  |

| bq4025    | 256Kx16 Nonvolatile SRAM                             | 6-81  |

| bq4285    | Real-Time Clock With NVRAM Control                   | 5-77  |

| bq4285E/L | Real-Time Clock With NVRAM Control, Enhanced         | 5-97  |

| bq4287    | Real-Time Clock Module With NVRAM Control            | 5-123 |

| bq4287E   | Enhanced Real-Time Clock Module With NVRAM Control   | 5-129 |

| bq4830Y   | Real-Time Clock Module With 32Kx8 NVSRAM             | 5-135 |

| bq4832Y   | Real-Time Clock Module With 32Kx8 NVSRAM             | 5-149 |

| bq4842Y   | Real-Time Clock Module With 128Kx8 NVSRAM            | 5-165 |

| bq4845/Y  | Parallel RTC With CPU Supervisor                     | 5-181 |

| bq4847/Y  | RTC Module With CPU Supervisor                       | 5-199 |

| bq4850Y   | Real-Time Clock Module With 512Kx8 NVSRAM            | 5-203 |

| bq4852Y   | Real-Time Clock Module With 512Kx8 NVSRAM            | 5-217 |

| DV2002L2  | bq2002 Linear Development System                     | 1-29  |

| DV2002TL2 | bq2002T Linear Development System                    | 1-29  |

| DV2003L1  | bq2003 Linear Development System                     | 1-43  |

| DV2003L3  | bq2003 Linear Development System                     | 1-45  |

| DV2003S1  | bq2003 Switching Development System                  | 1-47  |

| DV2003S2  | bq2003 Switching Development System                  | 1-49  |

| DV2004L1  | bq2004 Linear Development System                     | 1-101 |

| DV2004L3  | bq2004 Linear Development System                     | 1-103 |

| DV2004S1  | bq2004 Switching Development System                  | 1-105 |

| DV2004S3  | Nickel/Li-Ion Development System                     | 1-107 |

| DV2004ES1 | bq2004E Switching Development System                 | 1-125 |

| DV2004ES3 | bq2004E Switching Development System                 | 1-127 |

| DV2005L1  | bq2005 Linear Development System                     | 1-143 |

| DV2005S1  | bq2005 Switching Development System                  | 1-147 |

| DV2005S3  | bq2005 Switching Development System                  | 1-151 |

| DV2007S1  | bq2007 Switching Development System                  | 1-185 |

| DV2031S1  | bq2031 Switching Development System                  | 1-223 |

| DV2043S7  | Level 2 Smart Charger With Dual Battery Selector     | 2-145 |

| DV2054S1  | bq2054 Fast Charge Development System                | 1-287 |

| EV2010    | bq2010 Evaluation System                             | 2-19  |

| EV2011    | bq2011 Evaluation System                             | 2-47  |

| EV2011J   | bq2011J Evaluation System                            | 2-87  |

| EV2011K   | bq2011K Evaluation System                            | 2-87  |

| EV2012    | bq2012 Evaluation System                             | 2-109 |

| EV2014    | bq2014 Evaluation System                             | 2-133 |

| EV2014x   | bq2014 and bq2004 Gas Gauge/Fast Charge Eval. System | 2-135 |

| EV2050    | bq2050 Power Gauge™ Evaluation Board                 | 2-219 |

| EV205x    | bq2050, bq2053, and bq2004E Li-Ion Eval. System      | 1-289 |

| EV2903    | bq2903 Evaluation System                             | 1-323 |

## Fast Charge IC Summary and Selection Guide

Benchmarq's Fast Charge ICs provide fast charge control, current regulation support, and pre-charge qualification and conditioning for rechargeable batteries.

- Fast charging and conditioning of nickel cadmium, nickel metal hydride, lead acid, lithium ion, or rechargeable alkaline batteries

- Flexible current regulation support:

- Frequency-modulated linear (lowest cost)

- Switch-mode (most efficient)

- Gating control (external regulator)

- Easily integrated into systems or as a stand-alone charger

- Direct LED outputs display battery and charge status

- ➤ Fast charge termination by delta temperature/ delta time, negative delta voltage, peak voltage detect, minimum current, maximum temperature, maximum voltage, and maximum time

- > Optional top-off and maintenance charging

- ➤ Discharge-before-charge option

- Variable-rate charging uses excess supply current to charge batteries during system operation

## **Fast Charge IC Selection Guide**

| Battery<br>Technology    | Charge<br>Control<br>Output | Termination Method                                            | Key<br>Features                          | Pins /<br>Package              | Part<br>Number | Page<br>Number |

|--------------------------|-----------------------------|---------------------------------------------------------------|------------------------------------------|--------------------------------|----------------|----------------|

| NiMH<br>NiCd             | Single                      | -ΔV, peak voltage, time                                       | Low power and small size                 | 8/.300" DIP,<br>8/.150" SOIC   | bq2002         | 1-1            |

| NiMH<br>NiCd             | Single                      | -ΔV, PVD, max. temp., time                                    | Low power and small size                 | 8/.300" DIP,<br>8/.150" SOIC   | bq2002C        | 1-11           |

| NiMH<br>NiCd             | Single                      | ΔΤ/Δt, max. temp., time                                       | Low power and small size                 | 8/.300" DIP,<br>8/.150" SOIC   | bq2002T        | 1-19           |

| NiMH<br>NiCd             | Single                      | -ΔV, ΔT/Δt, max. temp.,<br>voltage, and time                  | Includes PWM                             | 16/.300" DIP,<br>16/.300" SOIC | bq2003         | 1-31           |

| NiMH<br>NiCd             | Single                      | -ΔV, peak voltage, ΔT/Δt,<br>max. temp., voltage,<br>and time | PWM and low-<br>power mode               | 16/.300" DIP,<br>16/.150" SOIC | bq2004         | 1-87           |

| NiMH, NiCd<br>Li-Ion     | Single                      | -ΔV, peak voltage, ΔΤ/Δt,<br>max. temp., voltage,<br>and time | PWM, pulsed<br>precharge<br>conditioning | 16/.300" DIP,<br>16/.150" SOIC | bq2004E        | 1-111          |

| NiMH<br>NiCd             | Dual                        | -ΔV, ΔT/Δt, max. temp., voltage, and time                     | Sequential<br>charger                    | 20/.300" DIP,<br>20/.300" SOIC | bq2005         | 1-131          |

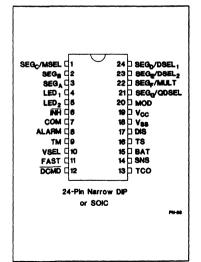

| NiMH<br>NiCd             | Single                      | -ΔV, peak voltage, max.<br>temp, voltage, and time            | LCD/LED<br>display                       | 24/.300" DIP,<br>24/.300" SOIC | bq2007         | 1-171          |

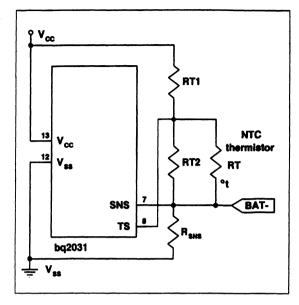

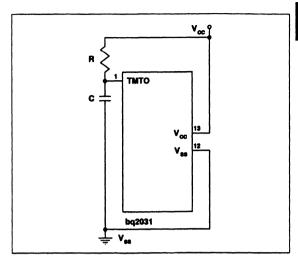

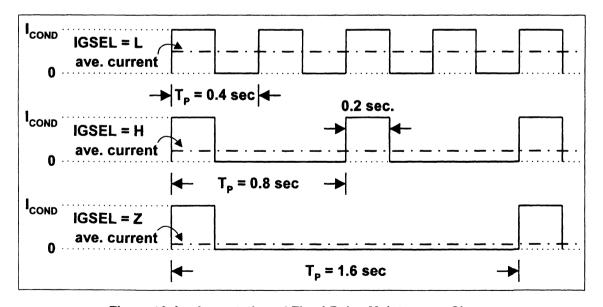

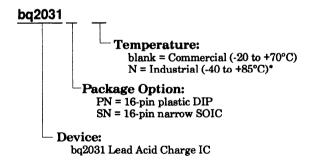

| Lead<br>Acid             | Single                      | max. voltage, min. current, $-\Delta^2$ V, temp., and time    | Temp. compensated thresholds             | 16/.300" DIP,<br>16/.150" SOIC | bq2031         | 1-209          |

| Lithium<br>Ion           | Single                      | max. voltage, min current                                     | 1% voltage<br>regulation                 | 16/.300" DIP,<br>16/.150" SOIC | bq2054         | 1-273          |

| Rechargeable<br>Alkaline | Single                      | maximum voltage                                               | 2-cell<br>charging                       | 8/.300" DIP,<br>8/.150" SOIC   | bq2902         | 1-305          |

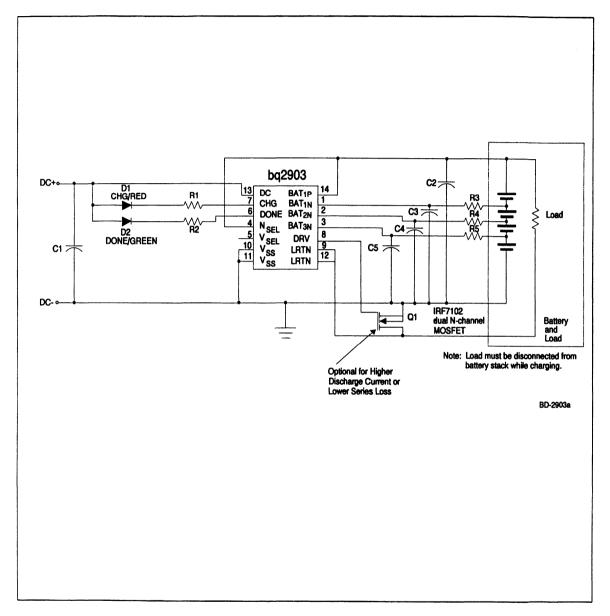

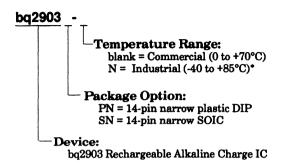

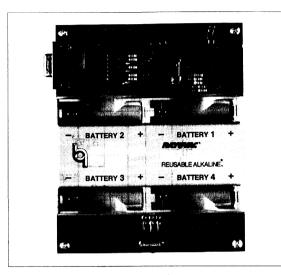

| Rechargeable<br>Alkaline | Single                      | maximum voltage                                               | 3- or 4-cell<br>charging                 | 14/.300" DIP,<br>14/.150" SOIC | bq2903         | 1-313          |

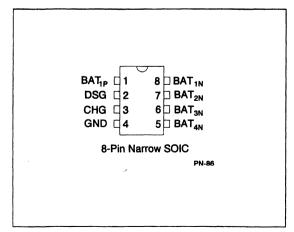

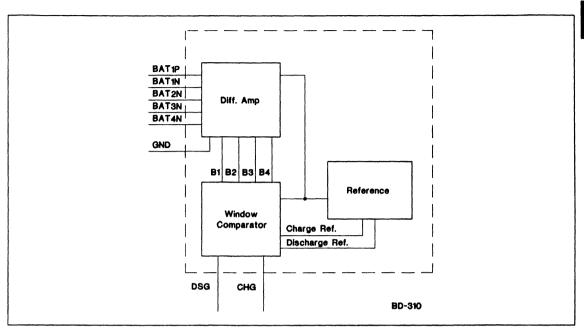

## **Pack Protection IC Summary and Selection Guide**

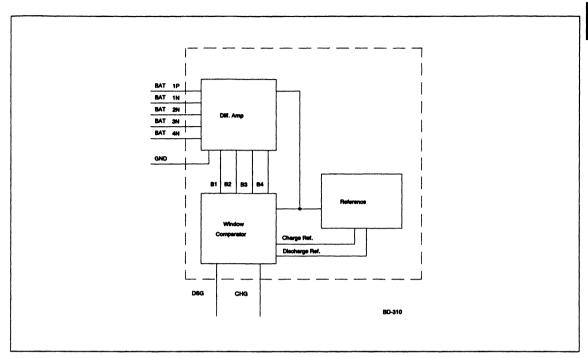

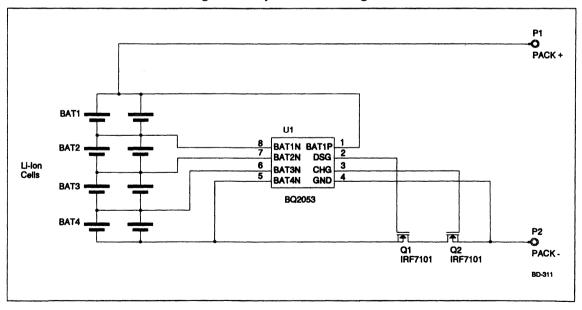

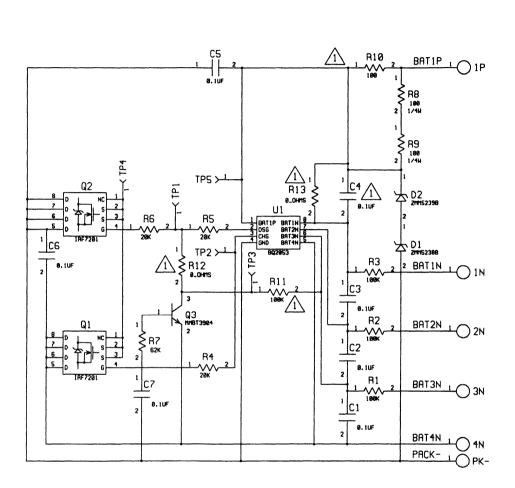

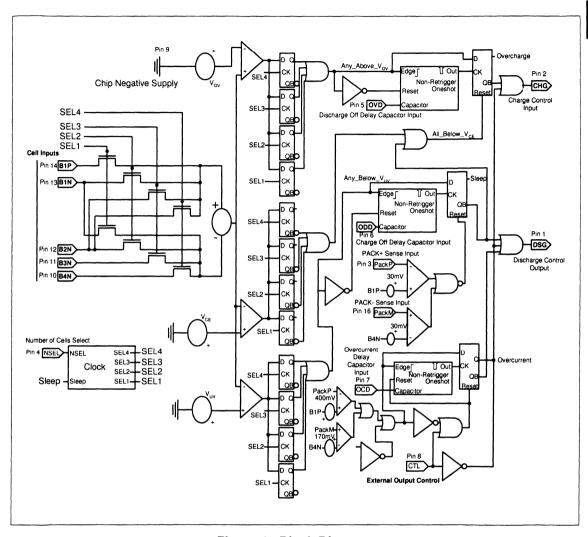

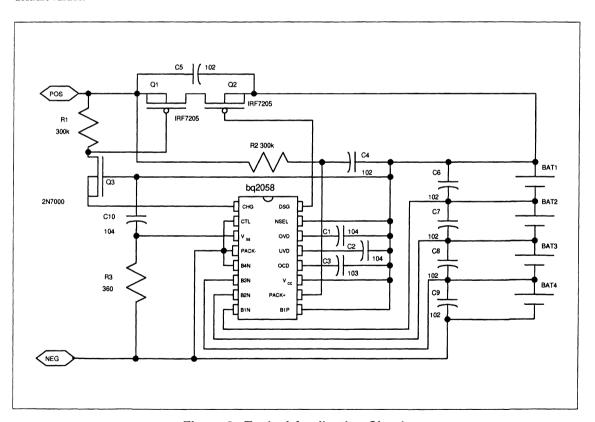

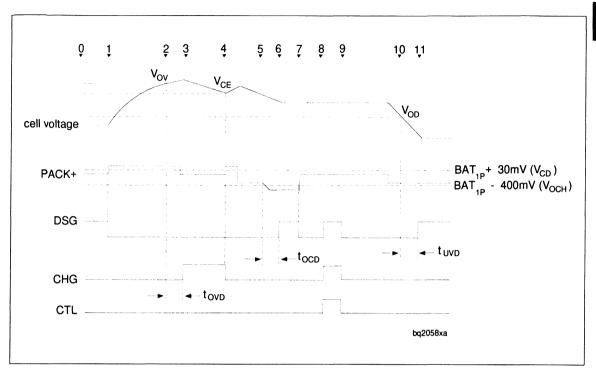

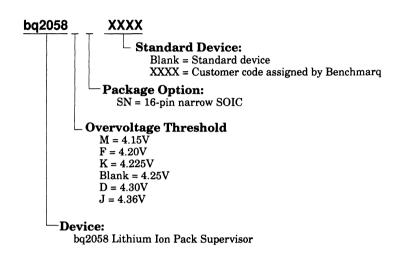

Benchmarq's bq2053 and bq2058 Lithium Ion Pack Protection ICs provide reversible overvoltage, undervoltage, and overcurrent protection for lithium ion battery packs.

- Protects two to four Lithium Ion series cells from overvoltage, undervoltage, and overcurrent

- Designed for battery pack integration

- Small outline package, minimal external components and space, and low cost

- Drives external N-FET switches

- User-selectable thresholds mask-programmable by Benchmarq

- ➤ bq2053 operating current:

- < 40μA for 4-cell configuration

- < 20μA for 3-cell configuration

- < 15μA for 2-cell configuration

- < 1µA sleep mode

- bq2058 operating current:

- < 60μA for 3-cell or 4-cell configuration</p>

## **Pack Protection IC Selection Guide**

| Battery<br>Technology | Protection Types                                 | Key<br>Features                | Pins /<br>Package | Part<br>Number | Page<br>Number |

|-----------------------|--------------------------------------------------|--------------------------------|-------------------|----------------|----------------|

| Lithium<br>Ion        | Overvoltage,<br>overcurrent, and<br>undervoltage | 2–4 cells<br>Very low power    | 8/.150" SOIC      | bq2053         | 1-257          |

| Lithium<br>Ion        | Overvoltage,<br>overcurrent, and<br>undervoltage | 3 or 4 cells<br>Very low power | 16/.150" SOIC     | bq2058         | 1-293          |

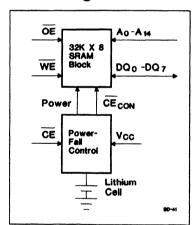

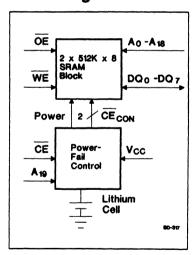

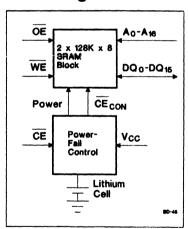

## **Nonvolatile SRAM Summary and Selection Guide**

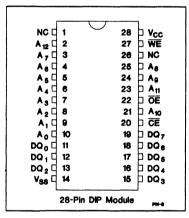

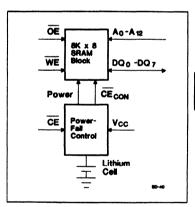

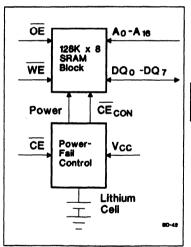

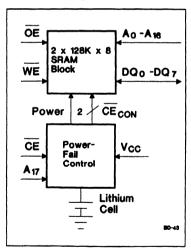

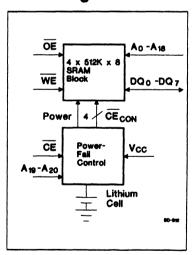

Benchmarq's NVSRAMs integrate—in a single-DIP package—extremely low standby power SRAM, nonvolatile control circuitry, and a long-life lithium cell. The NVSRAMs combine secure nonvolatility (more than 10 years in the absence of power) with standard SRAM pinouts and fast unlimited read/write operation.

- > Data retention in the absence of power

- ➤ Automatic write-protection during power-up/power-down cycles

- > Industry-standard pinout

- Conventional SRAM operation; unlimited write cycles

- > 10 or 5 years minimum data retention in the absence of power

- > Battery internally isolated until power is first supplied

- ➤ Industrial temperature range available

## **Nonvolatile SRAM Selection Guide**

| Density       | Config-<br>uration | Tech-<br>nology | Access<br>Time (ns)                           | Minimum Data-<br>Retention Time | Pins /<br>Package | Part<br>Number <sup>1</sup> | Page<br>Number |

|---------------|--------------------|-----------------|-----------------------------------------------|---------------------------------|-------------------|-----------------------------|----------------|

| 64 Kb         | 8 Kb x 8           | NVSRAM          | 70, 85 <sup>2</sup> , 150 <sup>2</sup> , 200  | 10 years                        | 28/DIP            | bq4010/<br>bq4010Y          | 6-1            |

| 256 Kb        | 32 Kb x 8          | NVSRAM          | 70 <sup>2</sup> , 100, 150 <sup>2</sup> , 200 | 10 years                        | 28/DIP            | bq4011/<br>bq4011Y          | 6-11           |

| 1 <b>M</b> b  | 128 Kb x 8         | NVSRAM          | 70 <sup>2</sup> , 85 <sup>2</sup> , 120       | 10 years                        | 32/DIP            | bq4013/<br>bq4013Y          | 6-21           |

| 0.34          | 256 Kb x 8         | NVSRAM          | 85, 120                                       | 10 years                        | 32/DIP            | bq4014/<br>bq4014Y          | 6-31           |

| 2 Mb          | 128 Kb x 16        | NVSRAM          | 85, 120                                       | 10 years                        | 40/DIP            | bq4024/<br>bq4024Y          | 6-71           |

| 435           | 512 Kb x 8         | NVSRAM          | 70, 85, 120                                   | 10 years                        | 32/DIP            | bq4015/<br>bq4015Y          | 6-41           |

| 4 Mb          | 256 Kb x 16        | NVSRAM          | 85, 120                                       | 5 years                         | 40/DIP            | bq4025/<br>bq4025Y          | 6-81           |

| 8Mb           | 1024 Kb x 8        | NVSRAM          | 70                                            | 10 years                        | 36/DIP            | bq4016<br>bq4016Y           | 6-51           |

| 16 <b>M</b> b | 2048 Kb x 8        | NVSRAM          | 70                                            | 5 years                         | 36/DIP            | bq4017<br>bq4017Y           | 6-61           |

Notes:

- 1. "Y" version denotes 10% Vcc tolerance.

- 2. "Y" version available in -40°C to +85°C industrial temperature range.

- 3. See data sheet for details.

## Nonvolatile Controller Summary and Selection Guide

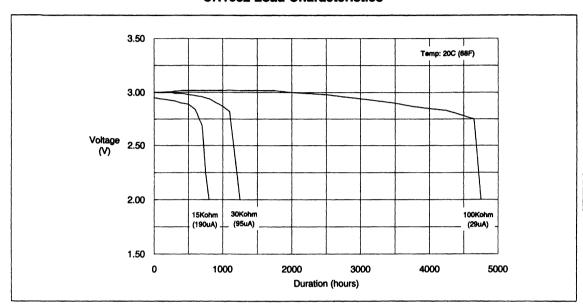

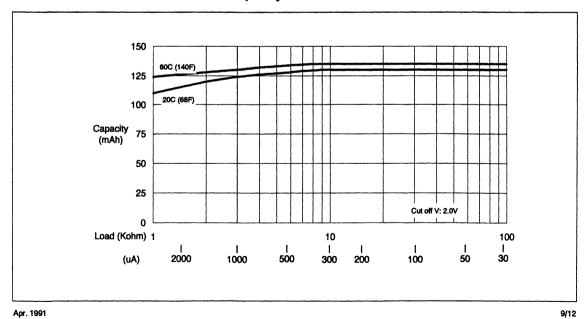

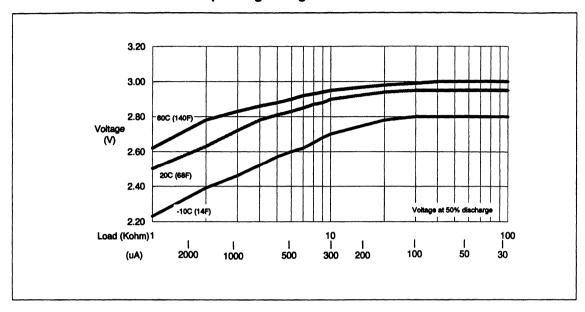

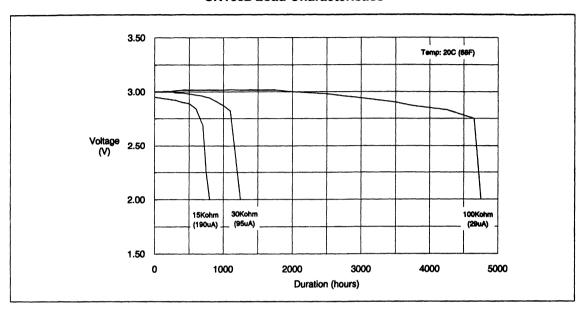

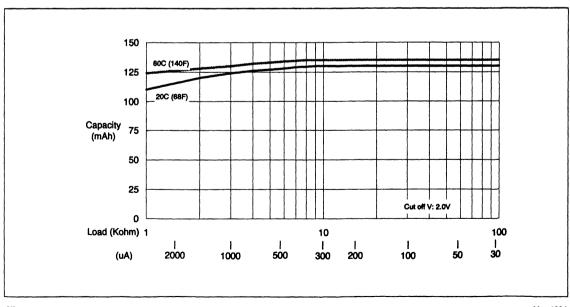

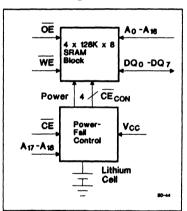

Benchmarq's nonvolatile controllers provide power monitoring, write-protection, and supply switching to convert standard SRAM or PSRAM and a backup battery into a reliable, predictable nonvolatile memory. The nonvolatile controller modules are complete battery-backup solutions including an encapsulated 130mAh lithium cell that is isolated until power is applied.

- Power monitoring and switching for 3V battery-backup applications

- ➤ 5V V<sub>CC</sub> operation

- ➤ Automatic write-protection during power-up/power-down cycles

- Automatic switching from V<sub>CC</sub> to first backup battery and from first backup battery to second backup battery

- > Reset output option for system power-on reset

- ➤ Less than 10ns chip enable propagation delay

- ➤ 5% or 10% supply operation

- ➤ Control up to four banks of SRAM

- Module/DIP or SOIC packages

## Nonvolatile Controller Selection Guide

| SRAM<br>Banks<br>Controlled | Battery<br>Monitor<br>Outputs | Reset<br>Output | lout<br>(Typ.) | Pins / Package | Part<br>Number | Page<br>Number |

|-----------------------------|-------------------------------|-----------------|----------------|----------------|----------------|----------------|

| 1                           |                               |                 | 160 mA         | 8/NDIP, NSOIC  | bq2201         | 4-1            |

| 2                           |                               | 1               | 160 mA         | 16/NDIP, NSOIC | bq2202         | 4-9            |

| 2                           | 1                             | 1               | 160 mA         | 16/NDIP, NSOIC | bq2203A        | 4-17           |

| 4                           |                               |                 | 160 mA         | 16/NDIP, NSOIC | bq2204A        | 4-25           |

| 2                           |                               | 1               | 160 mA         | 12/DIP module  | bq2502         | 4-33           |

## **Real-Time Clock Summary and Selection Guide**

Benchmarq's real-time clocks (RTCs) provide highly integrated clock/calendar solutions for microcomputer-based designs. Each *module* is a completely self-contained unit, including IC, crystal, and a battery ensuring operation for 10 years in the absence of power. The very compact, low-power *ICs* need only a battery and a crystal for operation. NVSRAM controller versions allow users to make inexpensive SRAM nonvolatile for data and configuration storage in computers, portable equipment, office machines and other applications.

- Clock/calendar counts seconds through years with daylight savings and leap-year adjustments

- ➤ IBM PC AT-compatible clocks include:

- 5- or 3-Volt operation

- 114 or 242 bytes of user nonvolatile RAM storage

- 32KHz output for power management

- Completely self-contained modules operate for more than 10 years in the absence of power

- SRAM-based clocks feature:

- SRAM interface

- Up to 512Kbytes of NVSRAM

- CPU Supervisor

- ➤ One minute per month clock accuracy in modules

- Nonvolatile control for an external SRAM

- ➤ IC versions require only a crystal and battery

## **Real-Time Clock Selection Guide**

| Onboard<br>RAM<br>(bytes) | NVRAM<br>Control | Bus<br>Interface | Voltage | 32kHz<br>Output | CPU<br>Super-<br>visor | Pins /<br>Package                  | Part<br>Number       | Page<br>Number |

|---------------------------|------------------|------------------|---------|-----------------|------------------------|------------------------------------|----------------------|----------------|

| 114                       |                  | Muxed            | 5V      |                 |                        | 24 / DIP, SOIC<br>28 / PLCC        | bq3285               | 5-1            |

| 242                       |                  | Muxed            | 5V      | 1               |                        | 24 / DIP, SOIC, SSOP<br>28 / PLCC  | bq3285E              | 5-21           |

| 242                       |                  | Muxed            | 5V      | 1               |                        | 24 / SOIC, SSOP                    | bq3285EC             | 5-45           |

| 242                       |                  | Muxed            | 3V      | 1               |                        | 24 / DIP, SOIC, SSOP               | bq3285L              | 5-21           |

| 242                       |                  | Muxed            | 3V      | 1               |                        | 24 / SOIC, SSOP                    | bq3285LC             | 5-45           |

| 114                       |                  | Muxed            | 5V      |                 |                        | 24 / DIP module                    | bq3287/<br>bq3287A   | 5-69           |

| 242                       |                  | Muxed            | 5V      | 1               |                        | 24 / DIP module                    | bq3287E/<br>bq3287EA | 5-73           |

| 114                       | 1                | Muxed            | 5V      |                 |                        | 24 / DIP, SOIC<br>28 / PLCC        | bq4285               | 5-77           |

| 114                       | 1                | Muxed            | 5V      | <b>\</b>        |                        | 24 / DIP, SOIC, SSOP,<br>28 / PLCC | bq4285E              | 5-97           |

| 114                       | ✓                | Muxed            | 3V      | 1               |                        | 24 / DIP, SOIC, SSOP               | bq4285L              | 5-97           |

| 114                       | <b>√</b>         | Muxed            | 5V      |                 |                        | 24 / DIP module                    | bq4287               | 5-123          |

| 114                       | 1                | Muxed            | 5V      | 1               |                        | 24 / DIP module                    | bq4287E              | 5-129          |

| 32K                       |                  | SRAM             | 5V      |                 |                        | 28 / DIP module                    | bq4830Y              | 5-135          |

| 32K                       |                  | SRAM             | 5V      |                 | ✓                      | 32 / DIP module                    | bq4832Y              | 5-149          |

| 128K                      |                  | SRAM             | 5V      |                 | 1                      | 32 / DIP module                    | bq4842Y              | 5-165          |

| 0                         | 1                | SRAM             | 5V      |                 | 1                      | 28 / DIP, SOIC                     | bq4845/Y             | 5-181          |

| 0                         | ✓                | SRAM             | 5V      |                 | ✓                      | 28 / DIP module                    | bq4847/Y             | 5-199          |

| 512K                      |                  | SRAM             | 5V      |                 |                        | 32 / DIP module                    | bq4850Y              | 5-203          |

| 512K                      |                  | SRAM             | 5V      |                 | 1                      | 36 / DIP module                    | bq4852Y              | 5-217          |

## **NVSRAM Cross-Reference**

| Density      | Dallas<br>Semiconductor | SGS-<br>Thomson | Benchmarq       |

|--------------|-------------------------|-----------------|-----------------|

| 0.175        | DS1225AB                | MK48Z08         | bq4010          |

| 64Kb         | DS1225AD/Y              | MK48Z18         | bq4010Y         |

|              | DS1230AB                | M48Z30          | bq4011          |

| 05017        | DS1230Y                 | M48Z30Y         | bq4011Y         |

| 256Kb        | DS1630AB                | -               | Contact factory |

|              | DS1630Y                 | -               | Contact factory |

|              | DS1245AB                | M48Z128         | bq4013          |

|              | DS1245Y                 | M48Z128Y        | bq4013Y         |

| 1 <b>M</b> b | DS1645AB                | •               | Contact factory |

|              | DS1645Y                 | -               | Contact factory |

|              | DS1645EE                | -               | Contact factory |

|              | -                       | M48Z256         | bq4014          |

|              | DS1249Y                 | M48Z256Y        | bq4014Y         |

| <b>2M</b> b  | DS1658AB                | M46Z128         | bq4024          |

|              | DS1658Y                 | M46Z128Y        | bq4024Y         |

| 440          | DS1650                  | M48Z512         | bq4015          |

|              | DS1650Y                 | M48Z512Y        | bq4015Y         |

| 4Mb          | -                       | M46Z256         | bq4025          |

|              | •                       | M46Z256Y        | bq4025Y         |

## **Real-Time Clock Cross-Reference**

| Dallas Semiconductor | SGS-Thomson | Benchmarq            |

|----------------------|-------------|----------------------|

| DS1285/885           | -           | bq3285P              |

| DS1285Q/885Q         | •           | bq3285Q              |

| DS1285S/885S         | •           | bq3285S              |

| DS1287/887           | MK48T87B24  | bq3287MT             |

| DS1287A/887A         | •           | bq3287AMT            |

| DS14285              | •           | bq4285P              |

| DS14285S             | •           | bq4285S              |

| DS14285Q             | •           | bq4285Q              |

| DS14287              | -           | bq4287MT             |

| DS1643               | M48T18      | bq4830Y <sup>1</sup> |

| DS1644               | -           | bq4830Y              |

| DS1646               | -           | bq4842Y <sup>2</sup> |

Notes:

- 1. Memory upgrade.

- 2. Benchmarq's bq4842 additional features: microprocessor reset, watchdog monitor, clock alarm, periodic interrupt.

## **Nonvolatile Controllers Cross-Reference**

| Dallas Semiconductor | Benchmarq                    |

|----------------------|------------------------------|

| DS1210               | bq2201PN <sup>4</sup>        |

| DS1210S              | bq2201SN <sup>1, 4</sup>     |

| DS1218               | bq2201PN <sup>5</sup>        |

| DS1218S              | bq2201SN <sup>5</sup>        |

| DS1221               | bq2204APN <sup>3, 4</sup>    |

| DS1221S              | bq2204ASN <sup>2, 3, 4</sup> |

Notes:

- 1. Benchmarq's bq2201SN is a small 8-pin, 150-mil SOIC, compared to the DS1210S, which is a 16-pin, 300-mil SOIC.

- 2. Benchmarq's bq2204ASN is a small 16-pin, 150-mil SOIC, compared to the DS1221S, which is a 16-pin, 300-mil SOIC.

- 3. Optional "security feature" DS1221 pins are no-connect on the bq2204A.

- Benchmarq's bq2201 and bq2204A do not incorporate a "check battery status" function.

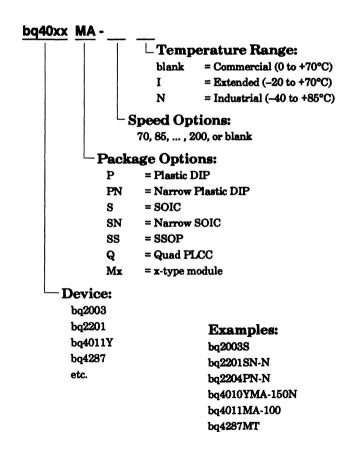

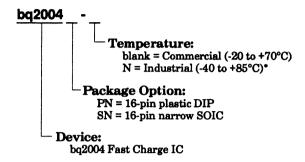

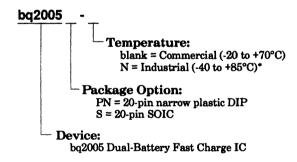

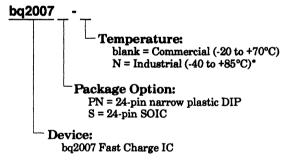

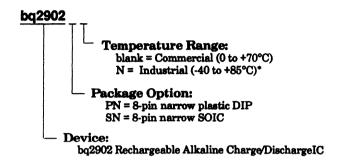

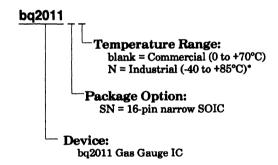

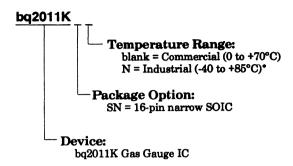

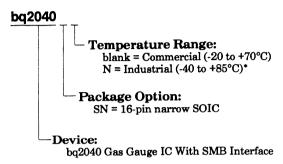

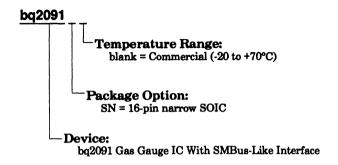

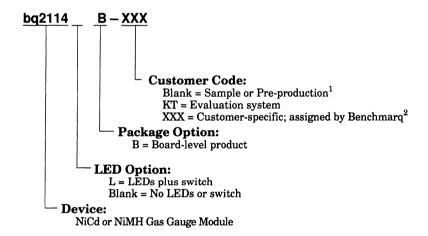

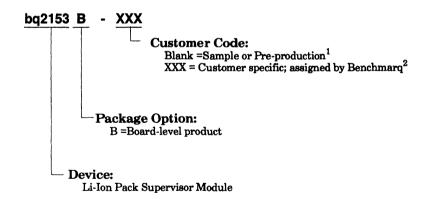

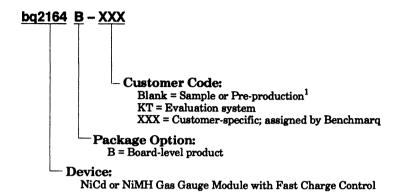

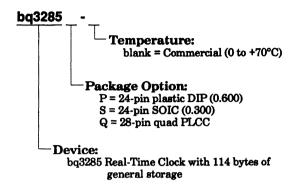

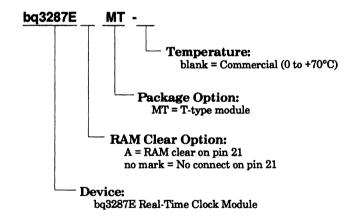

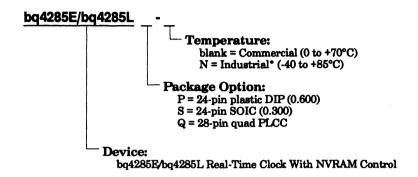

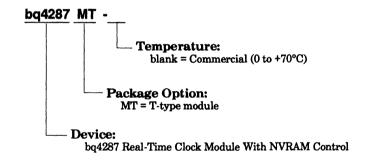

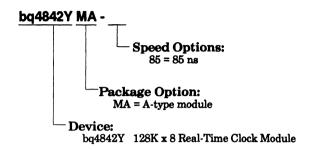

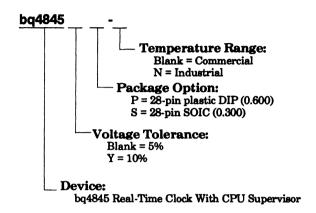

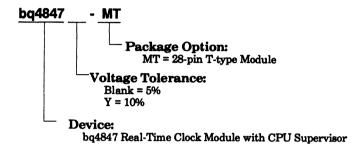

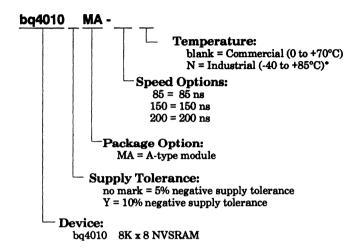

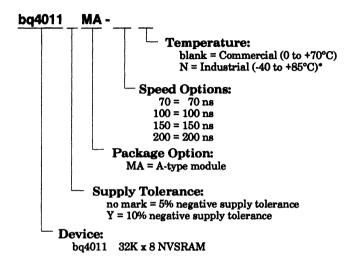

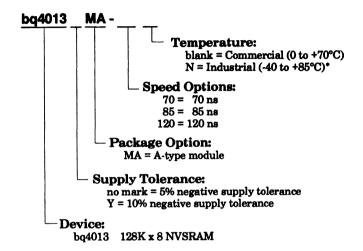

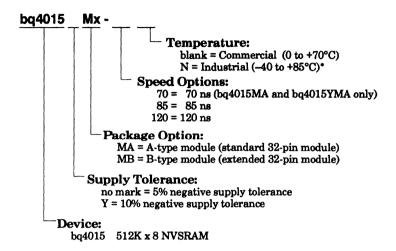

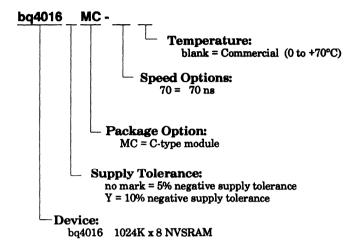

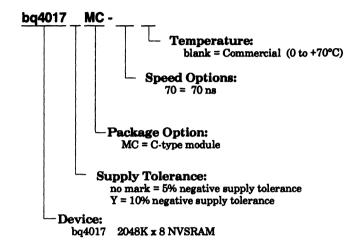

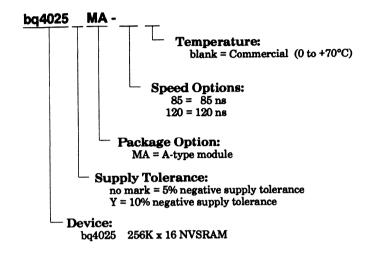

Benchmarq's standard products are available in several packages and operating ranges. A valid order number is a sequence of:

- Device

- Package Options

- Speed Options

- Temperature Range

Valid options for a specific device are defined in the ordering information section at the end of its data sheet. Contact your Benchmarq sales office about non-standard requirements or to place an order. Sales offices are listed at the end of this data book.

## **Data Sheet Types**

Product information data sheets progress in detail as the product goes from design to full production.

The three types of data sheets are defined below.

- Advance Information: Benchmarq Advance Information data sheets provide information for early product planning. These data sheets describe a product in the design or development stage. Specifications may change in any manner.

- Preliminary: Benchmarq Preliminary data sheets provide preliminary specifications for product design. They describe a product through its early production stage. Supplementary data may be published at a later date.

- Final: Benchmarq data sheets not labeled Advance Information or Preliminary are considered Final. They describe a product in full production and provide specifications for product design.

Benchmarg reserves the right to make changes to any products without notice.

## **Engineering Prototype**

Prior to full production, Benchmarq may provide limited quantities of Engineering Prototypes. Engineering Prototypes are suitably tested for evaluation and restricted use. Any necessary errata data accompanies engineering prototype parts. They are marked with the part number and are identified as Engineering Prototypes.

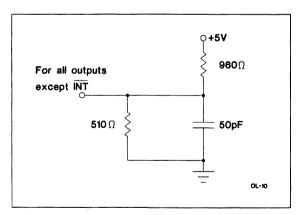

# Electrostatic Discharge (ESD) and Integrated Circuit (IC) Handling

Benchmarq ICs, as all ICs, are sensitive to electrostatic discharge (ESD). Although Benchmarq ICs are designed to withstand high ESD voltages, improper handling may cause damage. Standard ESD-prevention handling procedures should be followed. ESD-prevention considerations include proper grounding of operators, work surfaces and chip-handling equipment; appropriately high relative humidity levels; and use of antistatic handling and packaging materials. The ICs should be stored and shipped in antistatic tubes. The antistatic tubes containing the ICs must be brought to the same potential as the work area/operator before the individual ICs are handled.

| Fast Charge ICs                    | 1 |

|------------------------------------|---|

| Gas Gauge ICs                      | 2 |

| Battery Management Modules         | 3 |

| Static RAM Nonvolatile Controllers | 4 |

| Real-Time Clocks                   | 5 |

| Nonvolatile Static RAMs            | 6 |

| Package Drawings                   | 7 |

| Quality and Reliability            | 8 |

| Sales Offices and Distributors     | 9 |

# Fast Charge IC 1

#### **Features**

- ➤ Fast charge of nickel cadmium or nickel-metal hydride batteries

- ➤ Direct LED output displays charge status

- > Fast charge termination by - AV, peak voltage detection (PVD), maximum temperature, and maximum time

- ➤ Internal band-gap voltage reference

- ➤ Optional top-off charge

- ➤ Selectable pulse trickle charge rates

- ➤ Low-power mode

- ➤ 8-pin 300-mil DIP or 150-mil SOIC

#### **General Description**

The bq2002 Fast Charge IC is a lowcost CMOS battery charge controller providing reliable charge termination for both NiCd and NiMH battery applications. Controlling a currentlimited or constant-current supply allows the bg2002 to be the basis for a cost-effective stand-alone or systemintegrated charger. The bq2002 integrates fast charge with optional top-off and pulsed trickle control in a single IC for charging one or more NiCd or NiMH battery cells.

Fast charge is initiated on application of the charging supply or battery replacement. For safety, fast charge is inhibited if the battery temperature and voltage are outside configured limits.

Fast charge is terminated by any of the following:

- Peak voltage detection (PVD)

- Negative delta voltage (-ΔV)

- **■** Maximum temperature

- Maximum time

After fast charge, the bg2002 optionally tops-off and pulse-trickles the battery per the pre-configured limits. Fast charge may be inhibited using the INH pin. The bq2002 may also be placed in low-standby-power mode to reduce system power consumption.

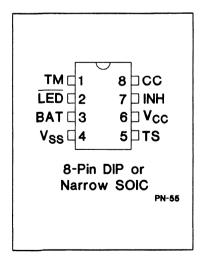

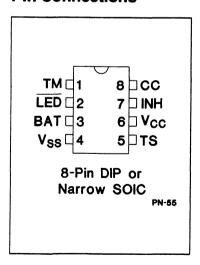

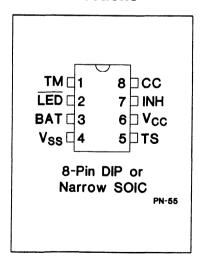

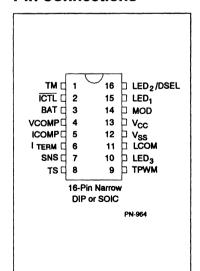

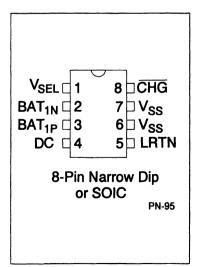

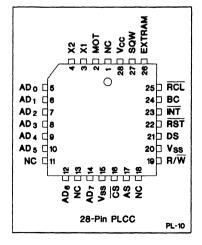

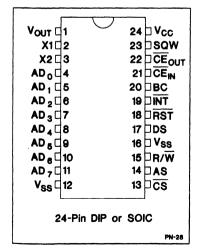

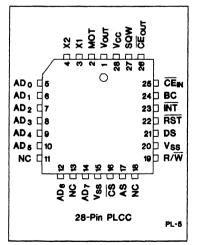

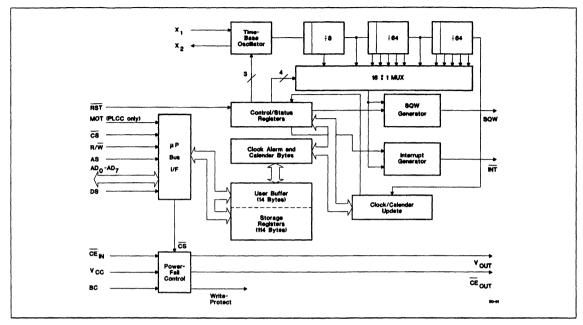

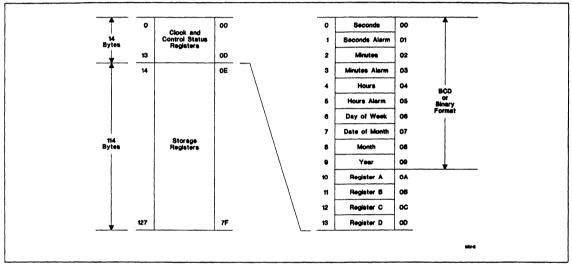

## **Pin Connections**

#### **Pin Names**

| TM         | Timer mode select input | TS  | Temperature sense input |

|------------|-------------------------|-----|-------------------------|

| <b>LED</b> | Charging status output  | Vcc | 5.0V ±20% power         |

| BAT        | Battery voltage input   | INH | Charge inhibit input    |

| $V_{SS}$   | System ground           | CC  | Charge control output   |

## **Pin Descriptions**

#### TM Timer mode input

TM is a three-level input that controls the settings for the fast charge safety timer, voltage termination mode, top-off, pulse-trickle, and voltage hold-off time.

#### LED Charging output status

This open-drain output indicates the charging status.

#### BAT Battery input voltage

BAT is the battery voltage sense input. This potential is generally developed by a high-impedance resistor divider network connected between the positive and negative terminals of the battery.

#### Vss System ground

#### TS Temperature sense input

This input is for an external battery temperature monitoring thermistor.

#### V<sub>CC</sub> V<sub>CC</sub> supply input

5.0V ±20% power input.

#### INH Charge inhibit input

When high, the bq2002 suspends the fast charge in progress. When returned low, the bq2002 resumes operation at the point where initially suspended.

#### CC Charge control output

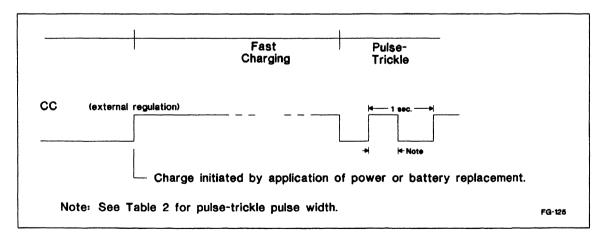

CC is an open-drain output that is used to control the charging current to the battery. CC switching to high impedance (Z) enables charging current to flow, and low to inhibit charging current. CC is modulated to provide top-off, if enabled, and pulse trickle.

## **Functional Description**

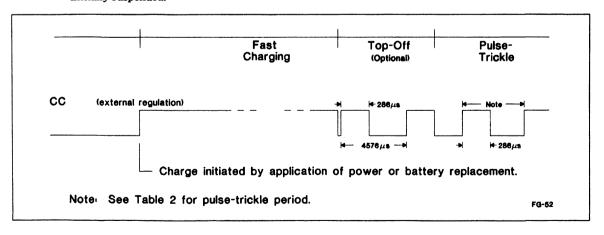

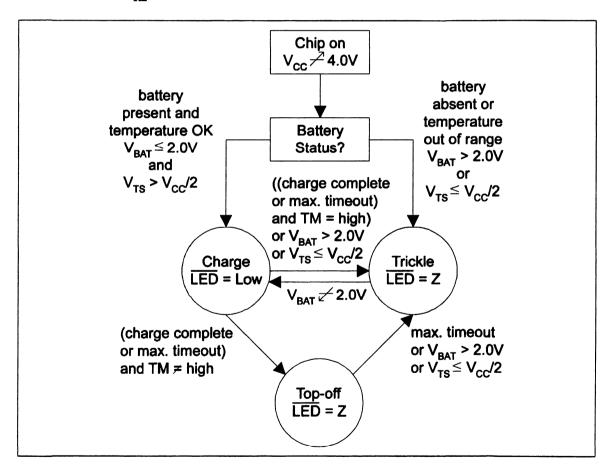

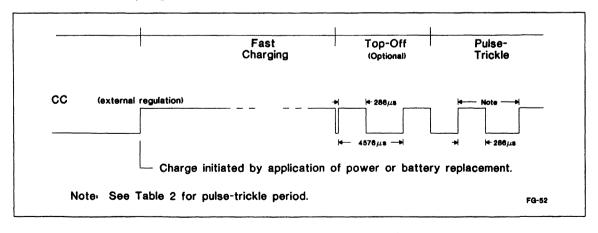

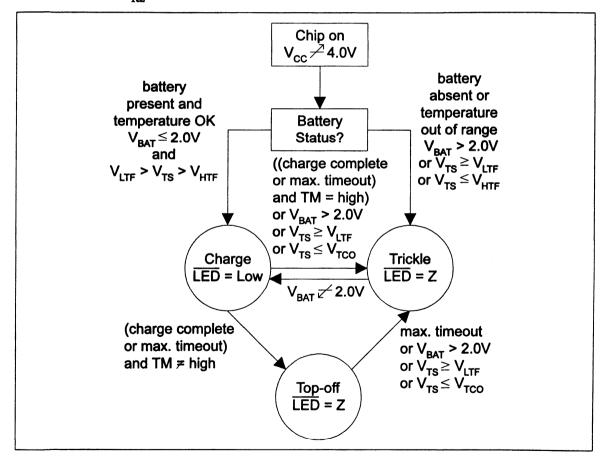

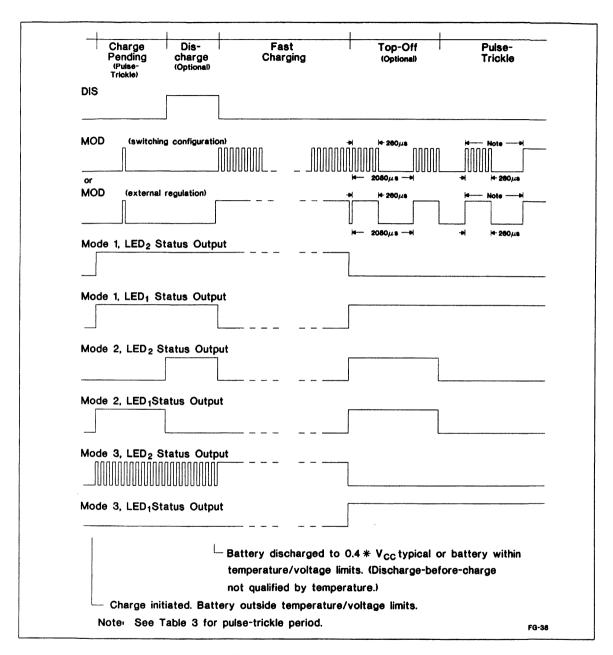

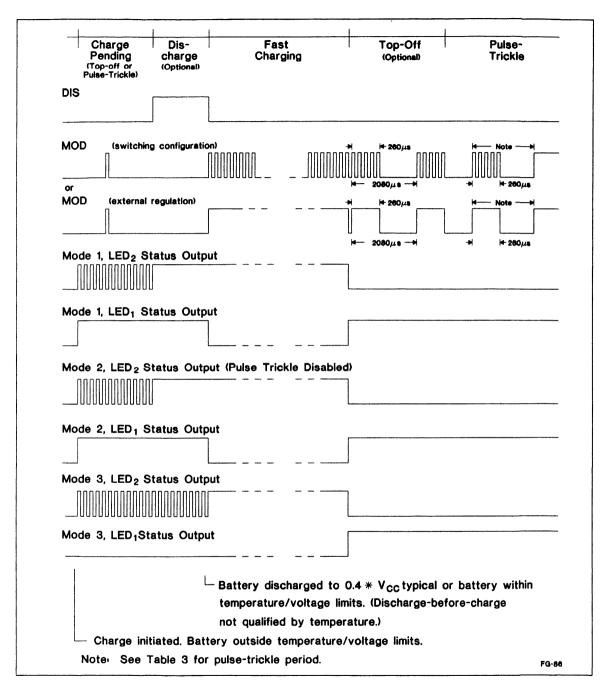

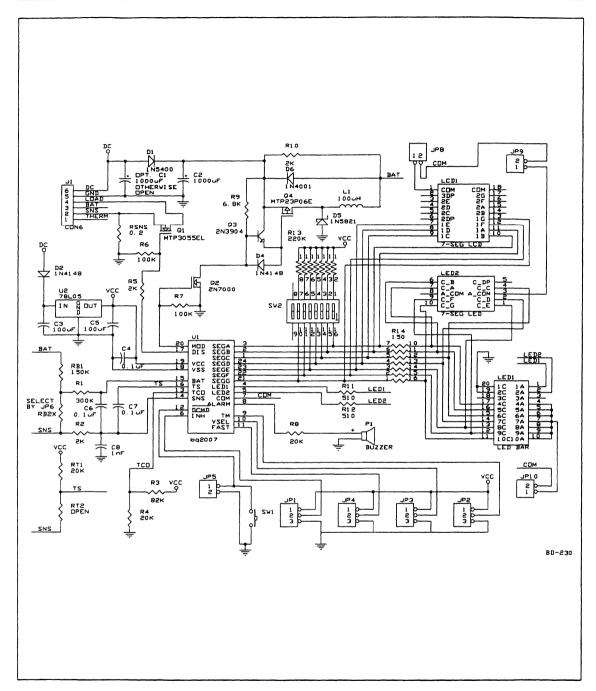

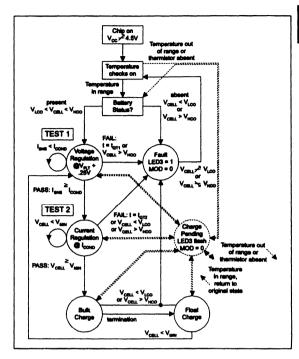

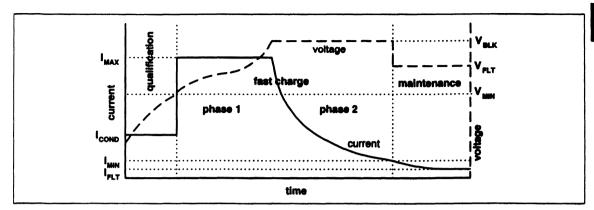

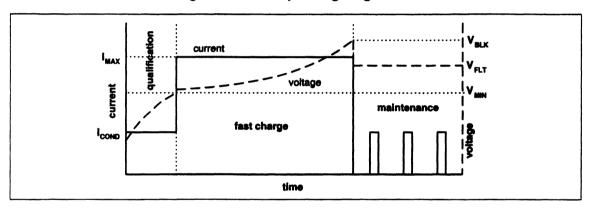

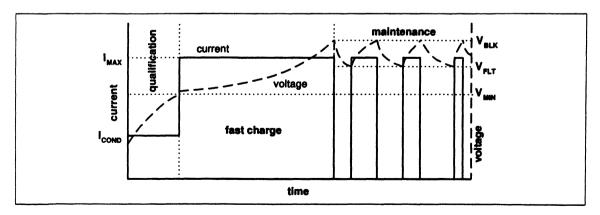

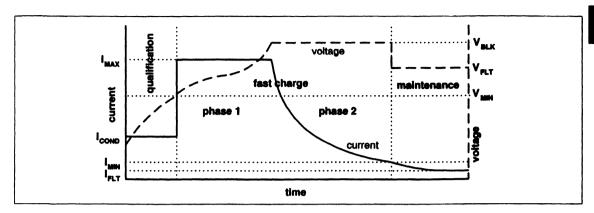

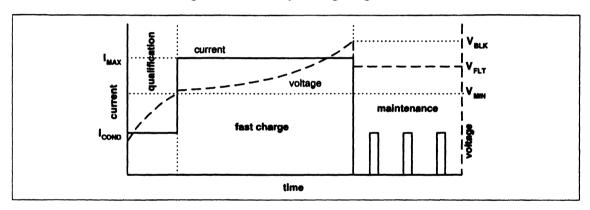

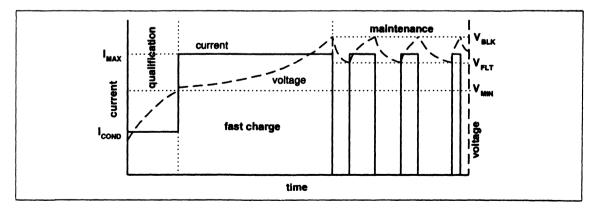

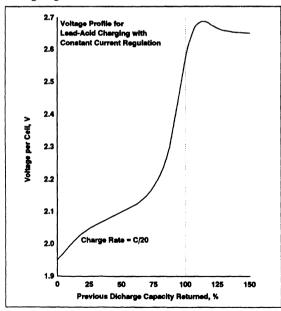

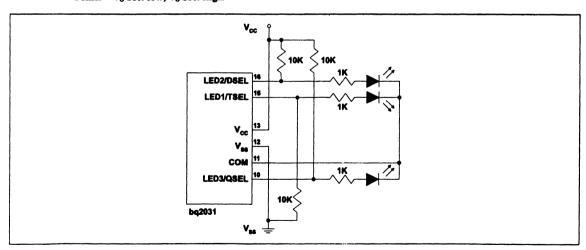

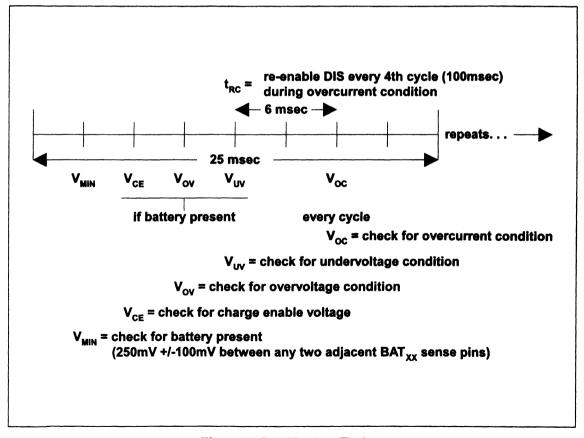

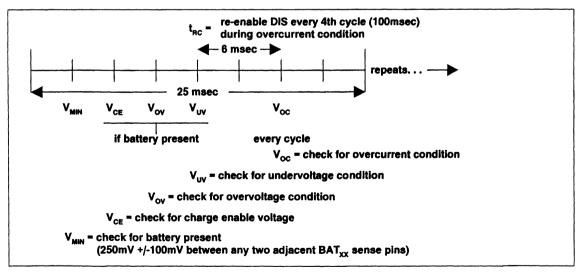

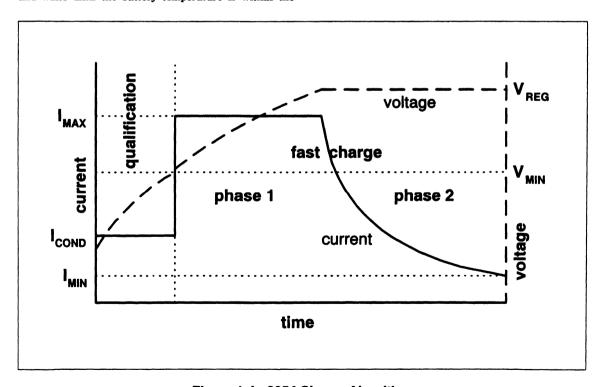

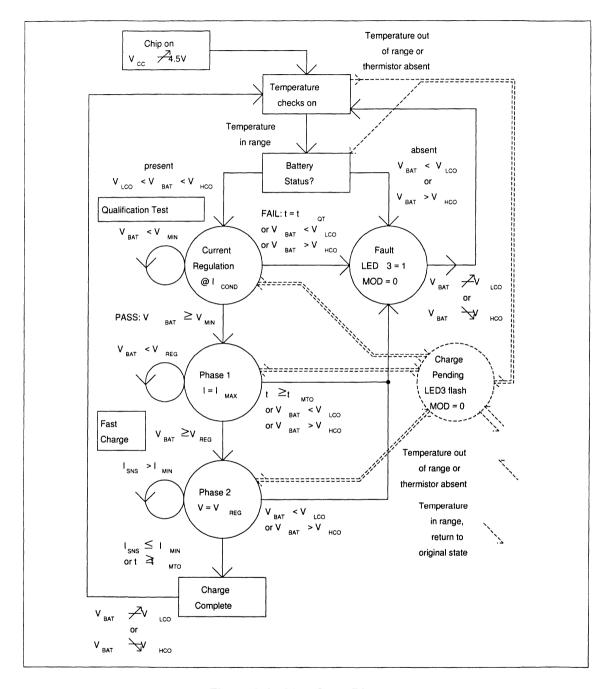

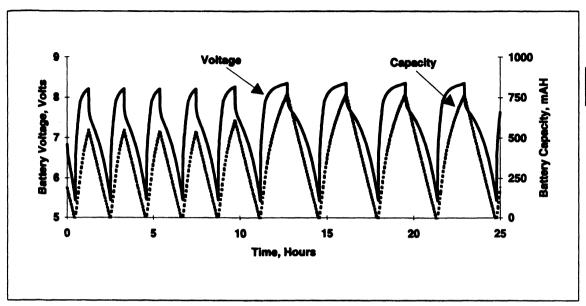

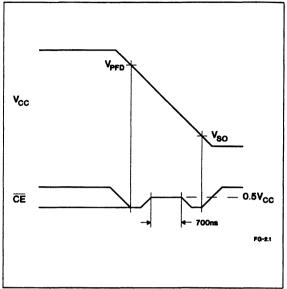

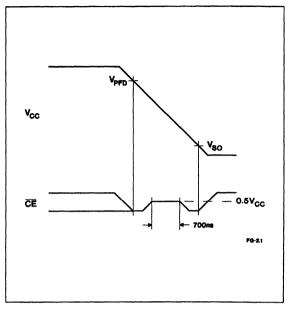

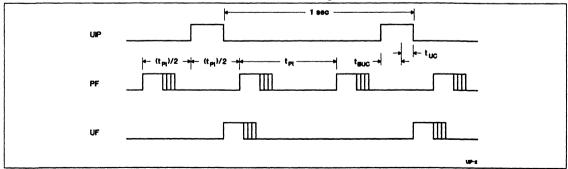

Figure 1 illustrates the charge control status during a bq2002 charge cycle. Figure 2 outlines the various bq2002 operational states and their associated conditions, which are described in detail in the following sections.

#### **Charge Action Control**

The bq2002 initiates a charge action by the application of power on Vcc or by battery replacement. Control of the charge action is then determined by inputs from TM, TS, and BAT.

Following charge initiation, the bq2002 checks for acceptable battery voltage and temperature. If the battery voltage or temperature is outside of the fast charge limits, pulse-trickle initiates at a rate determined by the TM pin. If the battery temperature and voltage are valid at charge initiation, fast charge begins.

The bq2002 then tests for the full-charge conditions:  $-\Delta V$ , PVD, maximum temperature, or maximum time.

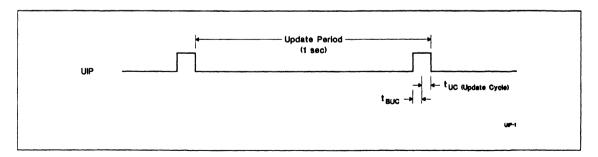

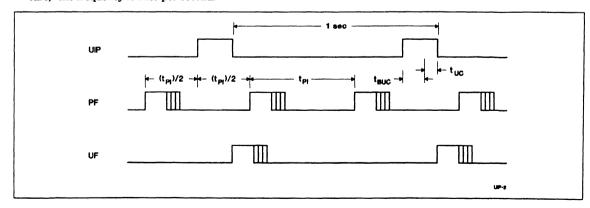

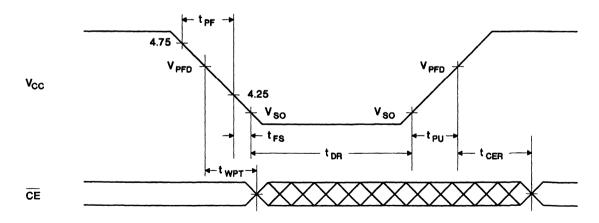

Figure 1. Example Charging Action Events

2/10

Sept, 1996 B

#### **Charge Status Indication**

A fast charge in progress is uniquely indicated when the LED pin goes low. The LED pin is driven to the high-Z state for all conditions other than fast charge. Figure 2 outlines the state of the LED pin during charge.

#### **Battery Voltage and Temperature Measurements**

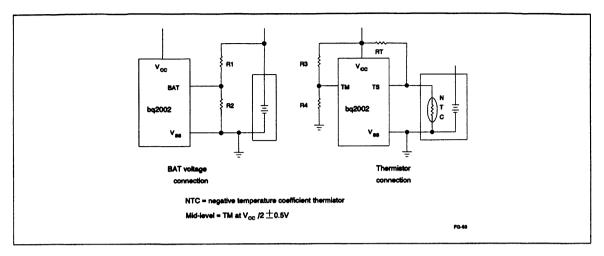

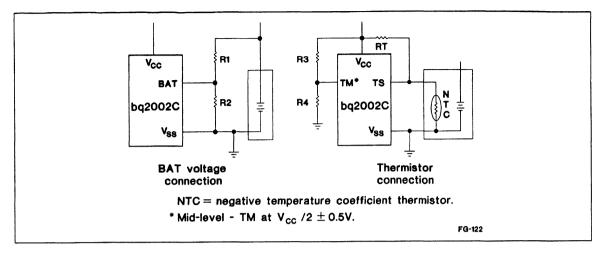

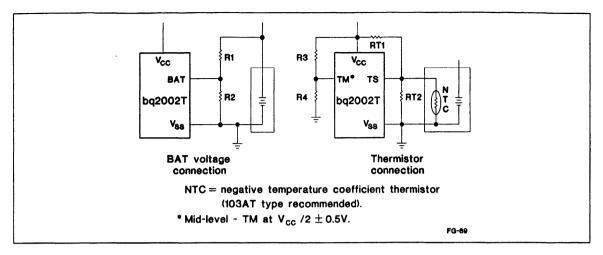

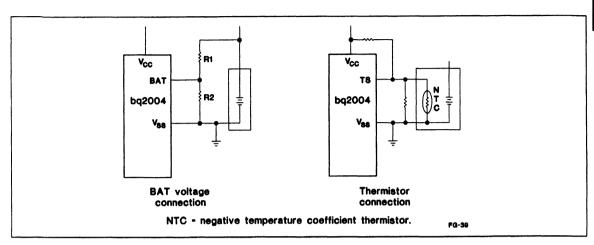

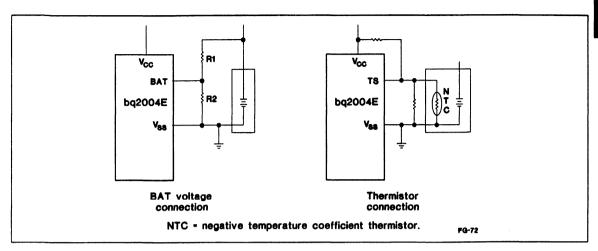

Battery voltage and temperature are monitored for maximum allowable values. The voltage presented on the battery sense input, BAT, should represent a single-cell potential for the battery under charge. A resistor-divider ratio of:

$$\frac{R1}{R2} = N - 1$$

is recommended to maintain the battery voltage within the valid range, where N is the number of cells, R1 is the resistor connected to the positive battery terminal, and R2 is the resistor connected to the negative battery terminal. See Figure 3.

Note: This resistor-divider network input impedance to BAT should be above  $200K\Omega$  to protect the bq2002.

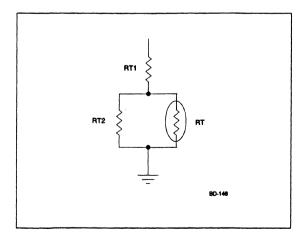

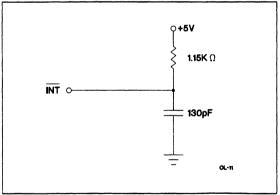

A ground-referenced negative temperature coefficient thermistor placed in close proximity to the battery may be used as a low-cost temperature-to-voltage transducer. The temperature sense voltage input at TS is developed using a resistor-thermistor network between Vcc and Vss. See Figure 3.

Figure 2. Operational Summary

Sept. 1996 B

Figure 3. Voltage and Temperature Limit Measurement

#### TM Pin

The TM pin is a three-level pin used to select the various charge timer, top-off, voltage termination mode, trickle rates, and voltage hold-off periods. Table 1 describes the various states selected by the TM pin. The mid-level selection input is developed by a resistor divider between VCC and ground. See Figure 3.

#### **Charge Initiation**

Application of power or battery voltage falling from above 2V initiates a charge action. If the battery is within the configured temperature and voltage limits, the bq2002 begins fast charge. The valid battery voltage range is BAT < 2V. The valid temperature range is TS >  $0.5 \cdot \text{Vcc}$ . If the battery voltage or temperature is outside of these limits, the bq2002 pulse-trickle charges until the next valid charge initiation.

The bq2002 continues to fast charge the battery until termination by one or more of the four possible termination conditions:

- Peak voltage detection (PVD)

- Negative delta voltage (-ΔV)

- Maximum time

- Maximum temperature (TCO)

$V_{\rm BAT} > V_{\rm MCV}$  stops fast charge or top-off.

#### **Voltage Termination Hold-off**

A hold-off time occurs at the start of fast charging. During the hold-off time, the PVD and -ΔV terminations are disabled (see Table 1). Once past the initial fast charge hold-off time, the PVD and -ΔV terminations are re-enabled. Maximum temperature is not affected by the hold-off period.

#### PVD and -AV Termination

The bq2002 has two modes for voltage termination depending on the state of TM. For standard  $-\Delta V$  (TM = high), if  $V_{BAT}$  is lower than any previously measured value by 12mV typical, the fast charge phase of the charge action is terminated. For PVD termination (TM = low or mid), a threshold of 0 to 5mV typical is used. The PVD and  $-\Delta V$  tests are valid for: 1V < BAT < 2V.

#### Maximum Time and Temperature

The bq2002 also terminates fast charge for maximum temperature (TCO) and maximum time. TCO reference levels provide the maximum limits for battery temperature during fast charge. If this limit is exceeded, then fast charge or optional top-off charge is terminated.

Maximum time selection is programmed using the TM pin. Time settings are available for corresponding charge rates of  ${}^{C}/{}_{2}$ , 1C, and 2C.

Sept. 1996 B

#### **Top-off Charge**

An optional top-off charge phase is selected to follow fast charge termination for 1C and ½ rates. This may be necessary to accommodate battery chemistries that have a tendency to terminate charge prior to achieving full capacity. With top-off enabled, charging continues after fast charge termination for a period of time selected by the TM pin (see Table 1). During top-off, the CC pin is modulated at a duty cycle of 286µs active for every 4290µs inactive. This results in an average rate ½6th that of the fast charge rate. Maximum time and temperature (TCO) terminations are the only methods enabled during top-off.

#### **Pulse-Trickle Charge**

Pulse-trickle is used to compensate for self-discharge while the battery is idle in the charger. The battery is pulse-trickle charged after fast charge or top off by driving the CC pin active for a period of 286µs for every 18.0ms of inactivity for 1C and 2C selections, and 286µs for every 8.86ms of inactivity for  $\frac{6}{2}$  selection. This results in a trickle rate of  $\frac{6}{6}$ 4 for the top-off enabled mode and  $\frac{6}{2}$ 50 otherwise.

#### Charge Inhibit

Fast charge and top-off may be inhibited by using the INH pin of the bq2002. When high, the bq2002 suspends all fast charge and top-off activity and the internal charge timer control. INH freezes the current state of LED until inhibit is removed. Temperature detection is not affected by the INH pin. During charge inhibit, the bq2002 continues to pulse-trickle charge the battery per the TM selection. When INH returns low, charge control and the charge timer resume from the point where INH went active.

#### **Low-Power Mode**

When BAT is driven above  $V_{PD}$ , the bq2002 assumes a low-power operational state. Both the CC pin and the  $\overline{\text{LED}}$  pin are driven to the high-Z state. The operating current of the bq2002 is reduced to less than 1 $\mu$ A in this mode. Subsequently, when BAT returns to a value below  $V_{PPD}$ , trickle charge is initiated.

Table 1. Fast Charge Safety Time/Hold-Off/Top-Off Table

| Corresponding<br>Fast Charge<br>Rate | TM   | Termination | Fast Charge<br>Top-off and<br>Safety<br>Time (minutes) | PVD and -∆V<br>Hold-Off<br>Time (seconds) | Top-Off          | Pulse-<br>Trickle<br>Rate | Pulsed<br>Trickle<br>Period<br>(ms) |

|--------------------------------------|------|-------------|--------------------------------------------------------|-------------------------------------------|------------------|---------------------------|-------------------------------------|

| C/2                                  | Mid  | PVD         | 160                                                    | 600                                       | C/32             | C/64                      | 9.14                                |

| 1C                                   | Low  | PVD         | 80                                                     | 300                                       | c/ <sub>16</sub> | C/64                      | 18.3                                |

| 2C                                   | High | -ΔV         | 40                                                     | 150                                       | Disabled         | C/32                      | 18.3                                |

Notes:

$T_A = 25$ °C,  $V_{CC} = 5.0$ V.

$Mid = 0.5 \cdot V_{CC}$

## **Absolute Maximum Ratings**

| Symbol   | Parameter Minimum Maximum                                                           |                      | Maximum     | Unit | Notes       |

|----------|-------------------------------------------------------------------------------------|----------------------|-------------|------|-------------|

| $V_{CC}$ | Vcc relative to Vss                                                                 | -0.3                 | +7.0        | V    |             |

| VT       | DC voltage applied on any pin excluding V <sub>CC</sub> relative to V <sub>SS</sub> | -0.3                 | -0.3 +7.0 V |      |             |

| Topr     | Operating ambient temperature                                                       | erature 0 +70 °C     |             | °C   | Commercial  |

| Tstg     | Storage temperature                                                                 | nperature -40 +85 °C |             | °C   |             |

| TSOLDER  | Soldering temperature                                                               | -                    | +260        | °C   | 10 sec max. |

| TBIAS    | Temperature under bias                                                              | -40                  | +85         | °C   |             |

Note:

Permanent device damage may occur if Absolute Maximum Ratings are exceeded. Functional operation should be limited to the Recommended DC Operating Conditions detailed in this data sheet. Exposure to conditions beyond the operational limits for extended periods of time may affect device reliability.

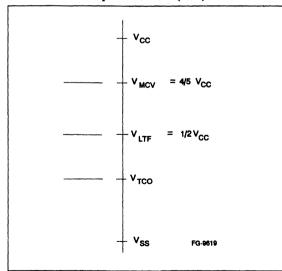

## DC Thresholds (TA = 0 to 70°C; VCC ±20%)

| Symbol           | Parameter            | Rating    | Tolerance | Unit | Notes                                                          |

|------------------|----------------------|-----------|-----------|------|----------------------------------------------------------------|

| V <sub>TCO</sub> | Temperature cutoff   | 0.5 • Vcc | ±5%       | v    | V <sub>TS</sub> ≤ V <sub>TCO</sub> inhibits charge             |

| V <sub>MCV</sub> | Maximum cell voltage | 2         | ±5%       | v    | V <sub>BAT</sub> > V <sub>MCV</sub> inhibits/terminates charge |

## Recommended DC Operating Conditions (TA = 0 to 70°C)

| Symbol           | Condition                      | Minimum                                      | Typical | Maximum                                      | Unit | Notes                                                                                                                            |

|------------------|--------------------------------|----------------------------------------------|---------|----------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------|

| Vcc              | Supply voltage                 | 4.0                                          | 5.0     | 6.0                                          | v    |                                                                                                                                  |

| V <sub>DET</sub> | -ΔV, PVD detect voltage        | 1                                            | -       | 2                                            | v    |                                                                                                                                  |

| VBAT             | Battery input                  | 0                                            | -       | Vcc                                          | v    |                                                                                                                                  |

| V <sub>TS</sub>  | Thermistor input               | 0.5                                          | -       | Vcc                                          | v    | TS < 0.5V prohibited                                                                                                             |

| V <sub>IH</sub>  | Logic input high               | 0.5                                          | -       | •                                            | v    | INH                                                                                                                              |

|                  | Logic input high               | V <sub>CC</sub> - 0.5                        | -       | -                                            | v    | ТМ                                                                                                                               |

| V <sub>IM</sub>  | Logic input mid                | $\frac{\mathrm{V_{CC}}}{2} - 500\mathrm{mV}$ | -       | $\frac{\mathrm{V_{CC}}}{2} + 500\mathrm{mV}$ | v    | тм                                                                                                                               |

| $V_{IL}$         | Logic input low                | -                                            | -       | 0.1                                          | v    | INH                                                                                                                              |

| VID.             | Logic input low                | -                                            | -       | 0.5                                          | v    | тм                                                                                                                               |

| Vol              | Logic output low               | •                                            | -       | 0.8                                          | v    | LED, CC, I <sub>OL</sub> = 10mA                                                                                                  |

| $ m V_{PD}$      | Power down                     | V <sub>CC</sub> - 1.5                        | -       | V <sub>CC</sub> - 0.5                        | v    | V <sub>BAT</sub> ≥ V <sub>PD</sub> max. powers<br>down bq2002;<br>V <sub>BAT</sub> < V <sub>PD</sub> min. =<br>normal operation. |

| $I_{CC}$         | Supply current                 | -                                            | -       | 250                                          | μА   | Outputs unloaded,<br>V <sub>CC</sub> = 5.1V                                                                                      |

| $I_{SB}$         | Standby current                | •                                            | -       | 1                                            | μA   | $V_{CC} = 5.1V$ , $V_{BAT} = V_{PD}$                                                                                             |

| $I_{OL}$         | LED, CC sink                   | 10                                           | -       | -                                            | mA   | $@V_{OL} = V_{SS} + 0.8V$                                                                                                        |

| IL               | Input leakage                  | -                                            | -       | ±1                                           | μА   | INH, CC, V = V <sub>SS</sub> to V <sub>CC</sub>                                                                                  |

| Ioz              | Output leakage in high-Z state | -5                                           | -       | •                                            | μА   | LED, CC                                                                                                                          |

Note: All voltages relative to Vss.

## Impedance

| Symbol | Parameter               | Minimum | Typical | Maximum | Unit |

|--------|-------------------------|---------|---------|---------|------|

| RBAT   | Battery input impedance | 50      | •       | •       | МΩ   |

| RTS    | TS input impedance      | 50      | •       | •       | MΩ   |

## Timing (TA = 0 to +70°C; VCC ±10%)

| Symbol | Parameter                         | Minimum | Typical | Maximum | Unit | Notes |

|--------|-----------------------------------|---------|---------|---------|------|-------|

|        | Fast charge safety time variation | 0.80    | 1.0     | 1.20    | •    |       |

Note: Typical is at  $T_A = 25$ °C,  $V_{CC} = 5.0$ V.

## **Data Sheet Revision History**

| Change No. | Page No. | Description                                                                                             | Nature of Change         |

|------------|----------|---------------------------------------------------------------------------------------------------------|--------------------------|

| 1          | 3        | Was: Table 1 gave the bq2002 Operational Summary.<br>Is: Figure 2 gives the bq2002 Operational Summary. | Changed table to figure. |

| 1          | 5        | Added Termination column to table and Top-off values.                                                   | Added column and values. |

Note: Change 1 = Sept. 1996 B changes from July 1994.

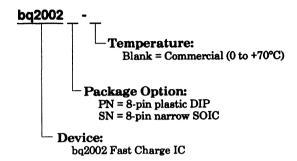

## **Ordering Information**

10/10 Sept. 1996 B

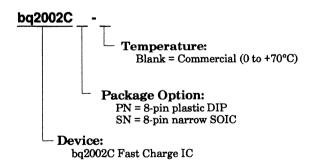

# Fast Charge IC 1

#### **Features**

- ➤ Fast charge of nickel cadmium or nickel-metal hydride batteries

- Direct LED output displays charge status

- Fast charge termination by

-ΔV, peak voltage detection

(PVD), maximum temperature,

and maximum time

- Selectable pulse trickle charge rates

- ➤ Low-power mode

- ➤ 8-pin 300-mil DIP or 150-mil SOIC

## **General Description**

The bq2002C Fast Charge IC is a low-cost CMOS battery charge controller providing reliable charge termination for both NiCd and NiMH battery applications. Controlling a current-limited or constant-current supply allows the bq2002C to be the basis for a cost-effective stand-alone or systemintegrated charger. The bq2002C integrates fast charge with pulsed trickle control in a single IC for charging one or more NiCd or NiMH battery cells.

Fast charge is initiated on application of the charging supply or battery replacement. For safety, fast charge is inhibited if the battery temperature and voltage are outside configured limits. Fast charge is terminated by any of the following:

- Peak voltage detection (PVD)

- Negative delta voltage (-ΔV)

- Maximum temperature

- Maximum time

After fast charge, the bq2002C pulse-trickle charges the battery according to the pre-configured limits. Fast charge may be inhibited using the INH pin. The bq2002C may also be placed in low-standby-power mode to reduce system power consumption.

## **Pin Connections**

### **Pin Names**

| TM  | Timer mode select input | TS  | Temperature sense input |

|-----|-------------------------|-----|-------------------------|

| LED | Charging status output  | Vcc | 5.0V ±20% power         |

| BAT | Battery voltage input   | INH | Charge inhibit input    |

| Vss | System ground           | CC  | Charge control output   |

## **Pin Descriptions**

#### TM Timer mode input

TM is a three-level input that controls the settings for the fast charge safety timer, voltage termination mode, pulse trickle, and voltage hold-off time.

#### LED Charging output status

This open-drain output indicates the charging status.

#### BAT Battery input voltage

BAT is the battery voltage sense input. This potential is generally developed by a high-impedance resistor divider network connected between the positive and negative terminals of the battery.

#### Vss System ground

#### TS Temperature sense input

This input is for an external battery temperature monitoring thermistor.

#### V<sub>CC</sub> V<sub>CC</sub> supply input

5.0V ±20% power input.

#### INH Charge inhibit input

When high, the bq2002C suspends the fast charge in progress. When returned low, the

bq2002C resumes operation at the point where initially suspended.

#### CC Charge control output

CC is an open-drain output that is used to control the charging current to the battery. CC switching to high impedance (Z) enables charging current to flow, and low to inhibit charging current. CC is modulated to provide pulse trickle.

## **Functional Description**

Figure 1 illustrates the charge control status during a bq2002C charge cycle. Table 1 outlines the various bq2002C operational states and their associated conditions, which are described in detail in the following sections.

#### **Charge Action Control**

The bq2002C initiates a charge action by the application of power on Vcc or by battery replacement. Control of the charge action is then determined by the inputs from TM, TS, and BAT.

Following charge initiation, the bq2002C checks for acceptable battery voltage and temperature. If the battery voltage or temperature is outside of the fast charge limits (charge pending), pulse-trickle initiates at a rate determined by the TM pin. If the battery temperature and voltage are valid at charge initiation, fast charge begins.

The bq2002C then tests for the full-charge conditions: -AV, PVD, maximum temperature, or maximum time.

Figure 1. Example Charging Action Events

2/8

Dec. 1995

#### **Charge Status Indication**

A fast charge in progress is uniquely indicated when the LED pin goes low. The LED pin is driven low for 500msec, then high-Z for 500msec during the charge pending state. The LED pin is driven to the high-Z state for charge complete. Table 1 outlines the state of the LED pin during charge.

#### **Battery Voltage and Temperature Measure**ments

Battery voltage and temperature are monitored for maximum allowable values. The voltage presented on the battery sense input, BAT, should represent a single-cell potential for the battery under charge. A resistor-divider ratio of:

$$\frac{R1}{R2} = N - 1$$

is recommended to maintain the battery voltage within the valid range, where N is the number of cells, R1 is the resistor connected to the positive battery terminal, and R2 is the resistor connected to the negative battery terminal. See Figure 2.

Note: This resistor-divider network input impedance to BAT should be above  $200 K\Omega$  to protect the bq2002C.

A ground-referenced negative temperature coefficient thermistor placed in close proximity to the battery may be used as a low-cost temperature-to-voltage transducer. The temperature sense voltage input at TS is developed using a resistor-thermistor network between Vcc and Vss. See Figure 2.

Table 1. bq2002C Operational Summary

| Charge Action<br>State | Conditions                                                                                                                    | CC<br>Output                                             | LED                       |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|---------------------------|

| Battery absent         | V <sub>BAT</sub> ≥ V <sub>MCV</sub>                                                                                           | Trickle charge activated for period specified in Table 2 | High Z                    |

| Charge initiation      | V <sub>CC</sub> applied, V <sub>BAT</sub> drops from ≥ V <sub>MCV</sub> to < V <sub>MCV</sub> (battery replaced)              | -                                                        | -                         |

| Charge pending         | V <sub>TS</sub> < V <sub>TCO</sub> or<br>V <sub>BAT</sub> < V <sub>LBAT</sub>                                                 | Trickle charge activated for period specified in Table 2 | 500ms low<br>500ms high-Z |

| Fast charging          | Charge initiation occurred and V <sub>TS</sub> > V <sub>TCO</sub> and V <sub>LBAT</sub> < V <sub>BAT</sub> < V <sub>MCV</sub> | High Z                                                   | Low                       |

| Charge complete        | -ΔV or PVD or maximum time<br>or maximum temperature <sup>1</sup>                                                             | -                                                        | High Z                    |

| Trickle                | Charge complete or<br>Charge Pend                                                                                             | Trickle charge activated for period specified in Table 2 | -                         |